- El ECC on-die de DDR5 corrige errores internos del chip DRAM, pero no sustituye al ECC de banda lateral que protege todo el trayecto de datos entre CPU y memoria.

- La memoria ECC clásica requiere módulos específicos y una plataforma (CPU y placa) compatible, y ofrece mayor fiabilidad a costa de un ligero impacto en rendimiento y precio.

- En PCs de consumo y gaming, la RAM sin ECC sigue siendo la opción más razonable, mientras que en servidores y cargas críticas se recomienda combinar DDR5 con ECC on-die y ECC de sistema.

La llegada de la memoria DDR5 ha traído consigo un término que está generando bastante confusión: el llamado ECC integrado en chip (on-die ECC) frente al ECC “real” de servidor. A simple vista parece que toda DDR5 lleva ECC, así que mucha gente piensa que ya no necesita módulos ECC tradicionales ni plataformas específicas… pero la realidad es bastante más matizada.

En este artículo vamos a desgranar con calma en qué se diferencia el ECC interno obligatorio en DDR5 del ECC clásico de banda lateral, qué papel juega la CPU, qué impacto tiene en coste, rendimiento y fiabilidad, y qué puedes esperar si estás montando un PC de juegos, una estación de trabajo o un servidor. La idea es quitar mitos de en medio y que puedas decidir con criterio sin perderte entre siglas.

Qué es realmente el ECC clásico y cómo funciona

Cuando se habla de “ECC real” en el mundo de los servidores, se suele hacer referencia a módulos de memoria que incorporan un chip extra para almacenar bits de paridad o códigos de corrección, más un controlador de memoria (en la CPU o en el chipset) capaz de entender y usar esa información adicional.

En los módulos ECC convencionales, ya sea en DDR3, DDR4 o DDR5, los datos de usuario van acompañados de varios bits extra que no ves ni puedes usar directamente, pero que sirven para detectar y corregir errores de un solo bit (y en algunos casos para detectar errores de más bits). Esta información de control viaja por un bus separado (banda lateral) y es procesada por la controladora de memoria.

El funcionamiento típico es sencillo de resumir: cada vez que la CPU escribe en memoria, el controlador genera un código ECC y lo guarda junto a los datos; cuando vuelve a leerlos, recalcula ese código y lo compara con el almacenado. Si hay una discrepancia pequeña (un bit cambiado), puede localizar qué bit se ha estropeado y corregirlo sobre la marcha antes de entregarlo a la CPU.

Este enfoque hace que la protección sea más amplia, porque la comprobación de errores cubre todo el trayecto desde el controlador de memoria hasta los chips DRAM: las líneas del bus, los conectores del módulo, el propio módulo e incluso parte de la lógica interna de la DRAM. Por eso, en entornos críticos (servidores, centros de datos, computación científica, bases de datos financieras, entrenamiento de IA) se utiliza memoria ECC como estándar de facto.

Qué es el ECC on-die de DDR5 y por qué es distinto

Con DDR5, todos los chips DRAM integran de fábrica un sistema de corrección de errores interno llamado On-Die ECC (ODECC). Esto ha llevado a mucha confusión, porque parece que “toda DDR5 incluye ECC”, pero no es lo mismo que un módulo ECC tradicional con bits de banda lateral visibles para la CPU.

El ODECC funciona dentro del propio chip de memoria: la DRAM almacena sus datos internos con un mecanismo de 128 bits de datos más 8 bits de código (128b+8b SEC), capaz de detectar y corregir errores de un solo bit a nivel de celda. La corrección se hace de forma transparente para el controlador de memoria, que ni siquiera ve esos bits extra ni participa en el proceso.

El objetivo principal de este ECC integrado no es proteger los datos de extremo a extremo, sino compensar el aumento de densidad y la fragilidad de las celdas DRAM modernas. Al subir capacidades, velocidades y reducir voltajes, los chips son más sensibles a interferencias y defectos internos; el on-die ECC permite mantener tasas de error aceptables y mejorar el rendimiento de fabricación (yield) sin que el usuario note nada.

Esto significa que, aunque todos los chips DDR5 usan ODECC, no todos los módulos DDR5 ofrecen protección ECC a nivel de sistema. Solo aquellos que añaden el bus de paridad extra y están conectados a una CPU y placa compatibles con ECC proporcionan la experiencia de “ECC de servidor” que conocíamos con DDR3/DDR4.

Diferencias clave entre ECC on-die y ECC de banda lateral

Para entender por qué no son equivalentes, conviene separar varios aspectos: ámbito de protección, coste, rendimiento y complejidad de implementación. De ese análisis sale por qué la industria ha hecho obligatorio el ODECC en DDR5 pero mantiene el ECC clásico como opción “premium”.

En lo que respecta al ámbito de protección, el ECC clásico de servidor protege los datos mientras viajan por el bus de memoria y mientras están almacenados en los chips DRAM. El on-die ECC, en cambio, solo actúa dentro de cada chip, y la CPU nunca ve ni controla esos bits extra; un error en el bus, en las pistas de la placa o en el conector del módulo no será detectado por el ODECC.

Desde el punto de vista del diseño, el on-die ECC permite a los fabricantes de DRAM usar celdas más pequeñas, trabajar con voltajes más bajos y densidades mayores sin disparar la tasa de fallos. La corrección se hace allí mismo, reduciendo la cantidad de módulos que habría que desechar en fábrica por pequeños defectos internos, algo muy relevante con densidades de 16, 24, 32 Gb y superiores.

En cambio, la corrección de errores de banda lateral necesita un bus de datos más ancho y un controlador de memoria más complejo. Esto encarece la plataforma y complica la validación, por lo que los fabricantes de CPU reservan esa característica para gamas profesionales (Xeon, EPYC, muchas Ryzen Pro, etc.), manteniendo diferenciados los productos de consumo y los de servidor.

En definitiva, el ODECC persigue asegurar la calidad básica del chip DDR5 y reducir costes de producción, mientras que el ECC clásico se orienta a garantizar la integridad de extremo a extremo en aplicaciones donde la corrupción de datos, por mínima que sea, es inaceptable.

Coste: por qué se ha impuesto el ECC on-die en DDR5

Una de las dudas más habituales es por qué el estándar DDR5 obliga a incluir ECC on-die pero no fuerza a que todas las CPUs soporten ECC de banda lateral. A primera vista podría parecer que añadir un chip extra en el módulo y usar el controlador ECC de la CPU no tendría por qué ser más caro, pero la situación real es distinta.

Por un lado, el ODECC es un coste que asumen los fabricantes de DRAM para mejorar el rendimiento de fabricación (yield). Al poder corregir internamente ciertos defectos de celda, se pueden vender como chips funcionales muchos dies que, sin ECC interno, habrían acabado descartados. Esto acaba abaratando el coste por gigabit y ayuda a que la DDR5 sea viable a las densidades objetivo.

Por otro lado, habilitar ECC clásico en todas las plataformas supondría añadir líneas extra en el bus de memoria, validación adicional, más capas de PCB en la placa base y un esfuerzo importante en soporte y pruebas para el fabricante de CPUs y placas. Todo ese coste se tendría que repercutir en productos donde, para la mayoría de usuarios domésticos, la ventaja es marginal.

Además, muchos procesadores de consumo comparten físicamente buena parte de la lógica con sus equivalentes de servidor, pero el soporte ECC se desactiva por segmentación de mercado. Es una forma clara de diferenciar el producto profesional del doméstico y poder cobrar un sobreprecio a las empresas que necesitan fiabilidad garantizada 24/7, algo que se aprecia especialmente en el mundo de los servidores x86 tradicionales.

Por tanto, desde el punto de vista de la industria, estandarizar el ODECC tenía sentido económico para garantizar yields aceptables en DDR5, mientras que universalizar el ECC clásico habría incrementado de forma notable los costes de plataforma sin un beneficio proporcional en el mercado masivo.

Rendimiento: impacto de ECC on-die frente a ECC de servidor

En cuanto a rendimiento, la creencia extendida es que el ECC tradicional introduce cierta penalización (en torno a un 2 % en muchos escenarios reales), mientras que el on-die ECC sería “gratis”. En la práctica, ambos añaden algo de sobrecarga, pero en capas distintas del sistema.

El ECC clásico trabaja a nivel de controlador de memoria, por lo que cada acceso debe calcular o verificar un código adicional. Esto incrementa muy ligeramente las latencias y el consumo, y además requiere un bus de datos algo más ancho, lo que complica alcanzar las máximas frecuencias absolutas en ciertos diseños de módulos.

El ECC on-die, en cambio, actúa dentro del chip DRAM y está muy optimizado para no penalizar el flujo normal de lecturas y escrituras. Los fabricantes lo integran con lógica dedicada y pipelines internos para que el impacto en la latencia efectiva sea muy pequeño, a cambio de una mayor complejidad del chip y de ocupar parte del silicio con el código ECC interno.

En sistemas de escritorio o gaming, donde se usan módulos sin ECC clásico, la diferencia de rendimiento entre DDR5 con ODECC y DDR5 sin ECC de banda lateral es prácticamente despreciable para el usuario. En plataformas de servidor, la penalización adicional de tener ambas cosas (ECC on-die + ECC clásico) es muy pequeña comparada con las ventajas de fiabilidad que se obtienen.

Por eso, en la práctica, la recomendación sigue siendo clara: si tu prioridad absoluta es la estabilidad y la integridad de los datos, el ligero coste en rendimiento de la memoria ECC compensa de sobra; si tu foco es el rendimiento puro en juegos o aplicaciones domésticas, la RAM sin ECC es suficiente y algo más rápida en igualdad de condiciones.

Fiabilidad: qué protege cada tipo de ECC y hasta dónde llega

La parte más delicada del debate es la fiabilidad. Mucha gente asume que, como DDR5 tiene ECC on-die, sus datos están plenamente protegidos contra errores de memoria, cuando en realidad solo se está mitigando un tipo muy concreto de fallo.

El ECC interno de DDR5 se centra en errores de bit dentro de las celdas de la DRAM, causados por interferencias electromagnéticas, radiación cósmica, fluctuaciones de voltaje u otros fenómenos físicos que llevan décadas siendo estudiados. Gracias al ODECC, muchos de estos fallos se corrigen al vuelo sin que ni el sistema operativo ni las aplicaciones lo detecten.

Sin embargo, la ruta de los datos no termina ahí. Desde que salen del controlador de memoria hasta que llegan a los chips DRAM, pasan por pistas en la placa base, contactos del socket, conectores del módulo, buses internos del DIMM… y todo ese trayecto no está cubierto por el on-die ECC. Un error en cualquiera de esos puntos puede alterar los bits antes de que lleguen al chip, y el ODECC no podrá distinguir si el dato recibido ya venía corrupto.

Es aquí donde entra el ECC tradicional con ancho de banda adicional: al generar el código ECC en el controlador de memoria y verificarlo cuando se lee de vuelta, se protege todo el enlace entre CPU y módulo, además de la propia DRAM. Por eso, cuando el requisito es máxima fiabilidad (finanzas, sanidad, investigación, almacenamiento crítico), las especificaciones técnicas exigen módulos ECC reales, no solo DRAM con on-die ECC.

Conviene también recordar que los módulos ECC permiten registrar o “loggear” los errores corregidos (diagnóstico de memoria RAM). Un servidor puede avisarte de que un DIMM está empezando a dar demasiados errores y conviene sustituirlo antes de que falle de forma irrecuperable. El ODECC, al ser transparente para el controlador, no te da visibilidad directa de esos fallos internos.

En resumen práctico: la DRAM DDR5 con on-die ECC es más robusta que la DDR4 sin ECC interno, pero si necesitas un sistema realmente resistente a fallos de memoria en todo el camino de los datos, sigues necesitando módulos ECC de banda lateral y una plataforma que los soporte.

Tipos de memoria ECC: RDIMM, UDIMM y “Registered EC8” en DDR5

En el entorno DDR4, la mayoría de usuarios que se interesaban por ECC se encontraban con dos grandes familias: ECC registrado o con búfer (RDIMM) y ECC sin búfer (UDIMM ECC). Cada una tiene su nicho, y con DDR5 la idea general se mantiene, aunque cambien algunos detalles técnicos.

Las memorias RDIMM incluyen un chip de registro o búfer entre el controlador de memoria y las celdas DRAM. Ese registro reduces la carga eléctrica sobre la CPU, permitiendo usar más módulos por canal y alcanzar mayores capacidades totales en servidores. A cambio, añaden algo de latencia y solo funcionan en placas base y procesadores que las soporten explícitamente.

Las UDIMM ECC, por su parte, se parecen mucho a los módulos de escritorio, pero con el chip extra de paridad. No llevan registro, lo que las hace más simples y con latencias muy parecidas a las de una RAM no ECC, pero su uso típico es en estaciones de trabajo y servidores ligeros que no necesitan enormes cantidades de memoria por canal.

Con DDR5 empiezan a verse fichas técnicas con términos como “Registered EC8”. En la práctica, esto indica que se trata de módulos registrados (RDIMM) que usan chips DDR5 con ODECC interno y una organización de 8 bits de código interno por cada 128 de datos. Es decir, combinan la corrección interna propia de DDR5 con el esquema clásico de módulo ECC de servidor.

Estos módulos son adecuados para servidores siempre y cuando la placa base y el procesador estén diseñados para trabajar con RDIMM DDR5 y en entornos que usan memoria persistente NVDIMM PMEM. En una plataforma de consumo genérica no funcionarán, igual que sucedía con las RDIMM DDR4. Si tu objetivo es montar un servidor doméstico o de laboratorio, debes fijarte muy bien en las compatibilidades: algunos procesadores solo aceptan UDIMM ECC, otros RDIMM, otros LRDIMM, etc.

Memoria ECC vs no ECC en PCs de consumo y gaming

Más allá de la discusión teórica, la pregunta práctica que se hacen muchos usuarios es si merece la pena montar memoria ECC en un PC de escritorio, para juegos o para uso general. Y con DDR5 en el mercado, la cosa parece aún más liosa.

En la informática cotidiana, la tasa de errores de memoria aleatorios que llegan a afectar de verdad a la experiencia de usuario es baja. Las DRAM modernas son bastante estables y la mayoría de fallos nunca se manifiestan como pantallazos azules o corrupción de datos visible. Por eso, la industria del PC de consumo ha estandarizado el uso de memoria sin ECC clásico durante años.

La memoria ECC introduce una ligera penalización de rendimiento, estimada tradicionalmente en torno a un 2 % en muchos escenarios, y tiene un precio más alto que la memoria no ECC. Cuando tu prioridad es exprimir unos cuantos FPS más en juegos o reducir costes en un PC doméstico, esa penalización y sobrecoste no se ven compensados por una fiabilidad que, en la mayoría de casos, no vas a notar.

Hay que añadir otro matiz importante: muchas placas base “gaming” aceptan físicamente módulos ECC, pero los tratan como si fueran módulos no ECC. Es decir, los instalas, el sistema arranca y funciona, pero la función de corrección de errores se desactiva y operan como RAM normal. Eso hace que pagar un extra por ECC en estas plataformas no tenga demasiado sentido, salvo que encuentres módulos de segunda mano muy baratos.

Con DDR5, recordemos que todos los chips llevan on-die ECC, tanto los módulos de consumo como los de servidor. Así que, incluso usando módulos no ECC clásicos en una plataforma doméstica, ya te estás beneficiando de cierta corrección interna a nivel de chip. Lo que sigues sin tener es protección de extremo a extremo ni registro de errores como en un servidor.

Cómo saber si tu sistema soporta memoria ECC

Si estás pensando en dar el salto a ECC, ya sea con DDR4 o DDR5, el primer paso es comprobar si tu CPU y tu placa base soportan realmente la corrección de errores. No basta con que el módulo sea ECC; la plataforma debe ser compatible de forma explícita.

Lo más fiable es ir a la web del fabricante de la placa base y revisar la ficha técnica: ahí suele indicarse si el modelo admite módulos ECC, si los usa en modo ECC o solo como no ECC, y qué tipo de módulos soporta (UDIMM ECC, RDIMM, LRDIMM, etc.). Esta información es clave para no llevarte sorpresas.

En cuanto al procesador, las gamas orientadas a empresa y servidor (Intel Xeon, AMD EPYC, muchas líneas Ryzen Pro) suelen ofrecer soporte ECC oficial. Algunos Ryzen de escritorio aceptan ECC con ciertas placas, aunque a veces el fabricante no lo certifica de forma completa. Intel, por su parte, reserva el ECC real casi siempre para Xeon y algunas plataformas específicas.

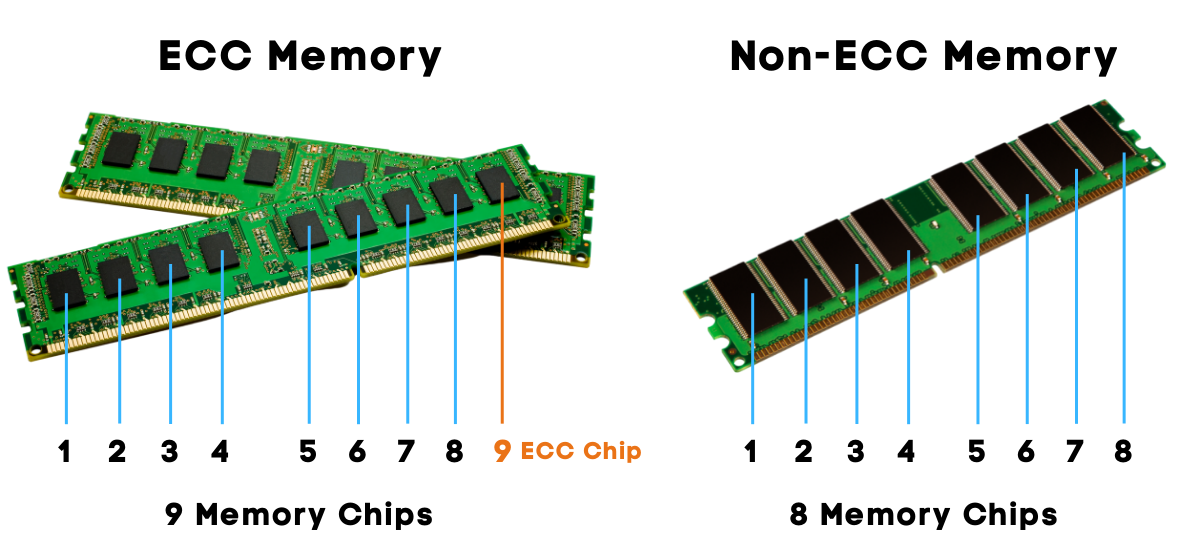

Un truco clásico para identificar módulos ECC es contar los chips negros del módulo: si el número total de chips es divisible por 9 (por ejemplo, 9, 18, etc.), suele tratarse de módulos con paridad o ECC, ya que ese chip extra aloja los bits de comprobación. Si no es divisible por 9, normalmente estás ante un módulo sin paridad.

Recuerda además que, si mezclas en el mismo sistema módulos ECC y no ECC, pueden darse problemas de arranque y, en el mejor de los casos, la función ECC se deshabilitará. El equipo puede seguir funcionando, pero perderás la corrección de errores incluso en los módulos que la soportan.

Características técnicas clave de DDR5 relacionadas con el ECC

DDR5 no solo introduce el ODECC; también cambia otros muchos aspectos de la arquitectura de la memoria que influyen en rendimiento, consumo y estabilidad. Para entender el contexto, conviene repasar algunas de las especificaciones más relevantes del estándar DDR5.

En cuanto a velocidad, DDR5 parte de tasas de datos muy superiores a DDR4, con perfiles que van desde 3600 MT/s hasta cifras que ya superan los 8400 MT/s y más allá. Esta ampliación de ancho de banda es una de las razones por las que ha sido necesario reforzar técnicas como la ecualización DFE (Decision Feedback Equalization) en la interfaz y el propio on-die ECC dentro de los chips.

En el plano eléctrico, DDR5 trabaja con tensiones nominales en torno a 1,1 V para VDD y VDDQ, y 1,8 V para VPP. Los módulos incorporan reguladores de voltaje integrados, lo que desplaza parte de la gestión de potencia desde la placa base al propio DIMM y ayuda a controlar mejor el consumo a frecuencias elevadas.

A nivel interno, la arquitectura de bancos crece: se manejan 32 bancos organizados en 8 grupos de bancos en muchas configuraciones, lo que mejora la paralelización de accesos. El prefetch es de 16n y se mantienen tamaños de página típicos de 1 KB (x4/x8) y 2 KB (x16), en línea con la evolución desde DDR3 y DDR4.

El estándar también introduce o mejora varias funciones de señalización y entrenamiento como la ecualización DFE en los canales de datos, la terminación on-die en DQ, DQS, DM y bus de comandos/direcciones, inversión de bus, “mirror pin” y modos dedicados de entrenamiento de lectura y escritura, incluyendo información sobre modos de gear 1 y 2. Todo esto ayuda a que, aunque las frecuencias y densidades suban, la señal mantenga una integridad aceptable.

En lo referente al ECC interno, el estándar especifica un esquema de 128 bits de datos + 8 bits de corrección (128b+8b SEC) para el ODECC, junto con mecanismos de CRC en lectura/escritura que refuerzan la detección de errores en la transferencia de datos. Son capas adicionales de protección pensadas para que la memoria pueda operar de forma fiable a los ritmos que exige el mercado actual.

Qué tener en cuenta al elegir memoria DDR5 hoy

Más allá del ECC, a la hora de comprar DDR5 entran en juego otros factores habituales: capacidad total, frecuencia, latencias y compatibilidad con tu plataforma. Un error de elección aquí pesa más en el día a día que debates teóricos sobre el ECC on-die.

En capacidad, DDR5 permite módulos mucho mayores que DDR4, con opciones que ya alcanzan decenas e incluso cientos de gigabytes por DIMM en entornos de servidor. Para un usuario doméstico, lo razonable hoy es partir de 16 GB para usos básicos (ofimática, navegación, multimedia) y subir a 32 GB o más si vas a jugar, virtualizar varias máquinas o trabajar con edición de vídeo y tareas pesadas.

La frecuencia efectiva (por ejemplo, DDR5-4800, DDR5-6000, DDR5-7200) marca el ancho de banda teórico. Cuanto más alta, mayor potencial de rendimiento de memoria, aunque las ganancias reales dependen del procesador y del tipo de aplicación. Si ves nomenclaturas tipo PC5-38400 o PC5-57600, basta dividir por 8 para obtener la frecuencia en MT/s.

Las latencias expresadas como CL40 o 40-40-40-77 indican el número de ciclos que tarda la memoria en responder a distintos tipos de comandos. Cuantos más bajos sean esos números, mejor en términos de latencia. Eso sí, hay que interpretarlos siempre junto a la frecuencia: una DDR5 muy rápida con un CL alto puede rendir parecido a otra algo más lenta pero con timings más ajustados.

También es importante fijarse en perfiles de overclock o ajustes automáticos: tecnologías como Intel XMP 3.0 o los perfiles equivalentes de AMD permiten que la placa configure la memoria a las frecuencias y latencias anunciadas por el fabricante sin tener que tocar decenas de parámetros a mano.

Y por último, revisa el tipo de módulo: DIMM para sobremesa, SO-DIMM para portátiles y equipos compactos. No son compatibles físicamente entre sí, así que conviene asegurarse antes de comprar. Algunos módulos traen disipadores de aluminio, útiles si vas a trabajar a frecuencias altas o en torres con poco flujo de aire.

La aparición del ECC on-die en DDR5 mejora la robustez interna de los chips y facilita que podamos tener memoria más rápida y con mayor capacidad sin disparar los fallos, pero no sustituye a la protección de extremo a extremo que aportan los módulos ECC clásicos en plataformas de servidor; si tu prioridad es la estabilidad absoluta, seguirás queriendo una combinación de DDR5 con ODECC más ECC de banda lateral, mientras que para un PC de juegos o de uso general la DDR5 estándar sin ECC de sistema, apoyada en su corrección interna, seguirá siendo la opción más lógica y equilibrada.