- Intel EMIB y EMIB-T son tecnologías de empaquetado avanzado basadas en puentes de silicio embebidos que permiten interconectar múltiples chiplets con alto ancho de banda sin recurrir a un interposer completo.

- La combinación de EMIB-T con Foveros Direct 3D y nodos como 18A y 14A permite a Intel escalar paquetes hasta el equivalente a 12 retículas, integrando numerosos tiles de cómputo y decenas de stacks de memoria HBM para cargas de IA extremas.

- Las negociaciones con Google y Amazon sitúan a Intel Foundry Services como alternativa real a TSMC en empaquetado avanzado, en un contexto donde la capacidad de CoWoS está saturada y el backend se ha convertido en cuello de botella.

- El empaquetado avanzado con EMIB-T ofrece ventajas de coste, flexibilidad de diseño, eficiencia energética y fabricación en EE. UU., lo que refuerza su atractivo estratégico en plena expansión de la IA y la reconfiguración de la cadena de suministro global.

La carrera por la inteligencia artificial ha cambiado por completo las reglas del juego en la industria de los semiconductores. Ya no basta con fabricar el chip más pequeño o el nodo más avanzado: ahora el foco está en cómo se interconectan y empaquetan varios chips dentro de un mismo sistema para exprimir al máximo el rendimiento, el ancho de banda y la eficiencia energética. En este nuevo tablero, Intel está intentando moverse rápido con una apuesta clara: convertir su tecnología de empaquetado avanzado, especialmente EMIB y su evolución EMIB-T, en una alternativa real y atractiva frente al dominio de TSMC.

Dentro de esta estrategia, las conversaciones de Intel con gigantes como Google y Amazon son algo más que simples negociaciones comerciales; representan un intento muy serio de posicionar a Intel Foundry Services como un actor imprescindible en el backend de la IA, justo en el punto donde se unen los chiplets de cómputo y la memoria HBM de alto ancho de banda. Vamos a desgranar qué es exactamente Intel EMIB-T, cómo funciona, en qué se diferencia de otras tecnologías como CoWoS o los interposers completos, y por qué puede convertirse en una pieza estratégica para acelerar la revolución de la inteligencia artificial.

Qué es Intel EMIB y qué añade EMIB-T

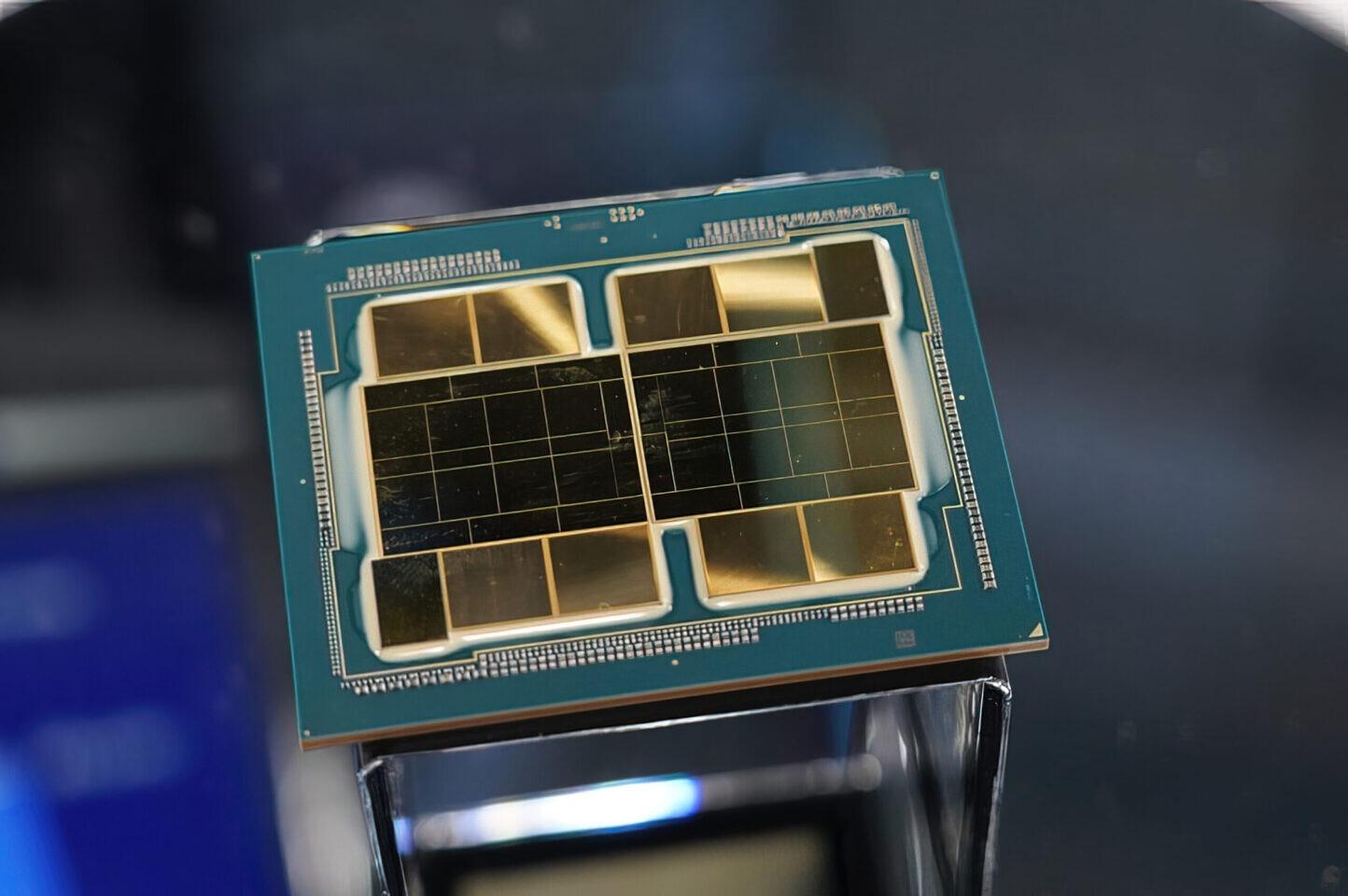

En esencia, EMIB (Embedded Multi-die Interconnect Bridge) es una técnica de empaquetado avanzado que permite unir varios chips o chiplets dentro del mismo encapsulado a través de pequeños puentes de silicio integrados en el propio sustrato. A diferencia de los interposers de silicio de tamaño completo, que ocupan toda la base del paquete y son caros y complejos, EMIB propone una solución más localizada: solo se coloca silicio allí donde hace falta interconexión de alta densidad.

Esta aproximación local tiene varias ventajas. Por un lado, reduce significativamente el coste frente a un interposer completo, y por otro mejora la flexibilidad de diseño al permitir conectar chiplets “de borde a borde” de forma selectiva. Así, se pueden combinar diferentes tipos de matrices (de cómputo, de I/O, de memoria, ASICs específicos, etc.) en un mismo paquete con un control más fino sobre el ancho de banda y las rutas de señal que realmente se necesitan.

EMIB-T es la evolución de esta tecnología. Según ha explicado la propia Intel, esta variante incorpora TSV (Through-Silicon Vias, o vías a través del silicio) en los puentes, lo que posibilita enlaces todavía más anchos y un enrutado más sofisticado para paquetes de gran tamaño con muchísimos componentes. Además, se ha trabajado en mejorar la integridad de la señal y la eficiencia energética entre los diferentes dies, algo clave cuando hablamos de aceleradores de IA de varios miles de vatios.

En la hoja de ruta de Intel, EMIB-T se presentó públicamente en mayo de 2025, con planes de despliegue industrial a partir de 2026. Justo en ese intervalo temporal es cuando empiezan a sonar con fuerza los rumores de acuerdos con Google y Amazon, lo que encaja con la necesidad urgente de estos clientes de encontrar capacidad de empaquetado avanzado que no esté saturada, como sí ocurre actualmente con buena parte de la oferta de TSMC.

Por qué el empaquetado avanzado es el nuevo campo de batalla de la IA

La industria se ha topado de frente con una limitación física: la llamada retícula del litógrafo. En la práctica, existe un tamaño máximo, alrededor de 830 mm² por exposición, que marca el tope de lo que puede ocupar un chip monolítico en un solo disparo de litografía. En segmentos como la IA o el HPC, donde se quiere juntar una barbaridad de núcleos de cómputo con memoria de altísimo ancho de banda, ese límite se ha convertido en un freno evidente.

La respuesta ha sido clara: dejar de pensar en un único chip gigante y pasar a arquitecturas modulares basadas en chiplets. En lugar de un solo trozo de silicio enorme, los diseñadores colocan varias matrices más pequeñas dentro del mismo paquete y las interconectan mediante tecnologías de empaquetado avanzado como CoWoS, EMIB o Foveros. El rendimiento ya no depende únicamente del nodo de fabricación, sino de cómo de bien estén unidos esos bloques entre sí.

TSMC domina actualmente este terreno con su tecnología CoWoS, muy utilizada por NVIDIA y otros grandes clientes para sus aceleradores de IA. Sin embargo, la demanda se ha disparado. La capacidad de CoWoS se ha convertido en un auténtico cuello de botella, hasta el punto de que muchos clientes están buscando alternativas simplemente para no tener toda su producción atascada en la misma cola. Es aquí donde Intel ve una oportunidad clara para colarse en el partido.

El empaquetado avanzado, además, se ha convertido en una actividad con márgenes altos dentro de la cadena de valor del chip. Para Intel, que tradicionalmente ha basado su negocio en fabricar sus propios procesadores, ofrecer servicios de empaquetado a terceros supone una vía directa para transformar su división de fundición en un negocio rentable, atrayendo clientes de primer nivel con productos muy demandados como los aceleradores de IA y los ASICs personalizados.

De hecho, desde la dirección financiera de la compañía se apunta a que los acuerdos previstos ya no se miden en cientos de millones, sino en miles de millones de dólares anuales, prueba de que el empaquetado avanzado ha pasado de promesa a pilar potencial de ingresos reales y sostenidos.

Cómo encaja EMIB-T en la estrategia de Intel Foundry Services

La apuesta de Intel no es solo técnica, sino también estratégica. La compañía intenta convencer al mercado de que su futuro no pasa únicamente por recuperar terreno en la fabricación de chips tradicionales, sino por ganar peso en esa parte menos visible pero cada vez más crítica: el backend y el empaquetado avanzado. Aquí es donde Intel Foundry Services (IFS) entra en escena con fuerza.

Intel lleva años desarrollando un ecosistema de tecnologías de empaquetado que combina EMIB para conexiones horizontales y Foveros para apilado 3D. La idea es poder ofrecer a clientes externos un conjunto coherente de soluciones que permitan integrar lógica de cómputo, chiplets especializados, interconexiones de alta densidad y memoria HBM dentro de un mismo paquete optimizado en coste, consumo y rendimiento.

En este contexto, las negociaciones con Google y Amazon encajan como un guante. Ambas compañías diseñan sus propios chips de IA y ASICs personalizados para sus centros de datos, pero externalizan la fabricación y muchas fases del backend. TSMC ha sido hasta ahora el gran referente, pero la saturación de su capacidad avanzada, especialmente con CoWoS, está generando tensiones que abren la puerta a que Intel se posicione como segunda gran opción real.

Importantísimo: Google y Amazon no tendrían por qué apostar por Intel para todo el proceso. Les bastaría con derivar a Intel la parte específica del empaquetado avanzado, por ejemplo el encapsulado con EMIB-T, si ven que esta pieza les resuelve un cuello de botella concreto que hoy tienen con TSMC. Esto reduce el riesgo para los clientes y, a la vez, permite a Intel ganar volumen y credibilidad en IFS.

Un antecedente relevante se conoció en septiembre de 2024, cuando Intel y AWS (Amazon Web Services) anunciaron una ampliación de su colaboración con un acuerdo multianual y multibillonario para chips personalizados, incluyendo un AI fabric chip en Intel 18A y un Xeon 6 personalizado en Intel 3. No se trataba todavía de un contrato de empaquetado avanzado, pero sí de una relación industrial ya consolidada y lista para escalar hacia servicios como EMIB o EMIB-T dentro de Intel Foundry Services.

La arquitectura por capas: más allá de la limitación de la retícula

Intel ha mostrado en un vídeo conceptual cómo imagina el futuro de sus paquetes para IA: una especie de “plataforma” modular capaz de superar el límite de la retícula sin recurrir a un único chip colosal. Según la propia compañía, la combinación de Foveros 3D con EMIB-T permitiría llegar hasta el equivalente a 12 retículas completas dentro de un solo paquete, integrando hasta 16 matrices de cómputo junto a 24 módulos de memoria HBM5.

La base de este diseño se construye sobre una variante del nodo 18A denominada 18A PT, que integra suministro de energía posterior (backside power). Esta técnica separa de forma más efectiva las rutas de potencia y de señal, lo que mejora tanto la densidad lógica como la fiabilidad. Esa base actuaría como “cimiento” del paquete, pudiendo albergar, por ejemplo, estructuras de SRAM similares a las previstas en diseños internos como Clearwater Forest.

Sobre dicha base se colocarían módulos de cómputo fabricados en nodos 14A y 14A-E, con transistores RibbonFET de segunda generación y una estrategia de entrega de energía denominada PowerDirect. La idea es que el paquete no sea simplemente “juntar chiplets sin más”, sino diseñar una arquitectura donde las rutas eléctricas y de potencia estén pensadas específicamente para cargas extremas de IA, con un comportamiento lo más coherente posible en latencia y consumo.

La compatibilidad declarada con HBM4, HBM5 y futuras generaciones refuerza el mensaje: se trata de un diseño orientado a trabajo intensivo de entrenamiento e inferencia masiva, donde el cuello de botella ya no está solo en la potencia de cálculo bruta, sino en el ancho de banda efectivo que se consigue entre matriz de cómputo y memoria de alta velocidad.

Foveros Direct 3D: apilado vertical con unión híbrida

El componente clave del apilado vertical en esta visión es Foveros Direct 3D. Intel se apoya aquí en una unión híbrida cobre con cobre, con pasos inferiores a 10 micras de separación entre interconexiones. Frente a soluciones con microbumps tradicionales, esto permite una densidad de contacto mucho mayor, menor resistencia y rutas más cortas.

En la práctica, más puntos de conexión y menor resistencia se traducen en que el conjunto de chiplets se comporta de forma más uniforme en términos de latencia, consumo y estabilidad térmica. En aceleradores de IA donde se dispara la potencia total del sistema, cada pérdida eléctrica termina convirtiéndose en calor, y cada vatio extra de calor implica costes mayores de refrigeración y límites de escalado.

Al integrar la lógica de cómputo en varias capas, Foveros Direct permite que algunas funciones se coloquen mucho más cerca físicamente, reduciendo las distancias eléctricas internas. Combinado con EMIB-T para las conexiones horizontales, se obtiene un enfoque híbrido donde el apilado vertical y los puentes de silicio trabajan juntos para maximizar el ancho de banda y minimizar penalizaciones.

Esta filosofía encaja especialmente bien con arquitecturas de IA en las que hay bloques muy especializados: motores de matriz, unidades de inferencia, bloques de comunicación, controladores de memoria HBM, etc. Repartirlos por capas y puentes de forma inteligente se convierte en una herramienta de diseño tan importante como la elección del nodo de fabricación.

EMIB-T: puentes de silicio para ancho de banda extremo

Si Foveros gestiona el “vertical”, EMIB-T se encarga del “horizontal”. Los puentes de silicio embebidos en el sustrato permiten unir chiplets de borde a borde con una densidad de interconexión muy alta, sin tener que recurrir a un interposer de silicio que cubra todo el paquete. Con la adición de TSV en EMIB-T, estos puentes ganan capacidad y versatilidad para paquetes de gran tamaño que integran decenas de componentes distintos.

Uno de los puntos donde mejor se entiende el valor de EMIB-T es en la integración de memoria HBM. La memoria de alto ancho de banda se ha convertido en el corazón de los aceleradores modernos, tanto o más importante que la propia lógica de cómputo. Ser capaz de colocar hasta 24 stacks de HBM5 junto a 16 tiles de cómputo y mantener un enlace ancho, eficiente y con pérdidas mínimas es justamente el tipo de reto que EMIB-T pretende resolver.

En lugar de un interposer gigantesco, EMIB-T ofrece un conjunto de puentes distribuidos que conectan cada grupo de chiplets o matrices con la porción de memoria que les corresponde. Eso permite adaptar mejor el diseño a las necesidades concretas de cada cliente, optimizando superficie, coste y complejidad del sustrato. No siempre se necesita el máximo ancho de banda absoluto: muchas veces es más valioso tener flexibilidad y disponibilidad inmediata de capacidad productiva.

Además, al estar integrado en el sustrato y apoyarse en TSV, EMIB-T facilita un enrutado más eficiente en paquetes muy grandes, evitando caminos enrevesados que penalizan señal y consumo. Esta arquitectura es especialmente atractiva cuando se combinan ASICs específicos, SoCs móviles, tiles de CPU o GPU y memoria HBM en una misma solución.

La propia Intel presenta EMIB-T como una vía más “quirúrgica” que las alternativas clásicas de interposer completo, con ahorros en espacio, mejoras en eficiencia y contención de costes a largo plazo para la carrera de la IA, justo lo que buscan clientes que necesitan escala masiva sin disparar el coste por chip.

El desafío de la potencia: GPUs de 5000 W y regulación integrada

En sus materiales, Intel llega a mencionar el objetivo de soportar una GPU de hasta 5000 vatios dentro de estos paquetes avanzados, con reguladores de voltaje integrados en el propio encapsulado. Este dato, que parece exagerado de primeras, refleja un problema muy real: la entrega de energía se está convirtiendo en un factor tan crítico como la propia lógica de cómputo.

El sector ya discute abiertamente aceleradores que superan los 2000 vatios de consumo, y algunos análisis sitúan en el horizonte productos que rozarán o superarán los 4000 vatios en futuras generaciones. A esas potencias, cualquier pérdida en la ruta de alimentación se traduce en calor extra, caída de eficiencia y mayores exigencias al sistema de refrigeración.

Integrar la regulación de voltaje dentro del paquete, acercándola físicamente al chip, acorta los caminos de corriente y reduce pérdidas. Intel relaciona esta visión con Foveros B, una evolución prevista en su hoja de ruta con objetivo de preparación para producción alrededor de 2027. Todo apunta a una convergencia entre empaquetado avanzado, distribución de potencia y diseño del propio silicio.

Para los grandes centros de datos de IA, este enfoque no es un simple detalle técnico. A escalas de miles o decenas de miles de aceleradores, cada punto porcentual de eficiencia energética cuenta. Un paquete que gestione mejor la potencia puede traducirse en ahorros millonarios en infraestructura, refrigeración y consumo eléctrico a lo largo del ciclo de vida del hardware.

Contexto geopolítico y capacidad: por qué EMIB importa en EE. UU.

Más allá de la parte tecnológica, el auge de EMIB y EMIB-T se entiende también desde la óptica geopolítica. En la actualidad, Estados Unidos apenas cuenta con instalaciones de empaquetado avanzado, más allá de las de Intel. Esto implica que muchos chips producidos, por ejemplo, por TSMC en Arizona tienen que viajar a Asia para completar el proceso de empaquetado, con todo lo que eso conlleva en coste, riesgo y plazos.

Para clientes estadounidenses que diseñan aceleradores de IA críticos para sus negocios, reducir esa dependencia logística se ha vuelto prioritario. EMIB y EMIB-T, fabricados y ensamblados en territorio estadounidense, ofrecen un flujo de producción mucho más directo y controlado, algo especialmente relevante en un contexto de tensiones comerciales y preocupación por la seguridad de la cadena de suministro.

Intel, por su parte, ha reforzado su colaboración con proveedores de sustratos en Japón y Taiwán, que están ampliando capacidad para anticipar una ola de pedidos masivos vinculados a estas tecnologías de empaquetado. Estos movimientos indican que EMIB está dejando de ser una promesa para convertirse en una solución asumida por clientes de primer nivel, con vistas a generar volúmenes importantes a partir de la segunda mitad de 2026.

Rumores del sector apuntan a que compañías como NVIDIA estudian seriamente EMIB para futuras familias de productos (como la rumoreada Feynman), mientras que otros actores como Apple, MediaTek o Qualcomm valoran esta vía para ciertos desarrollos donde importe equilibrar coste, flexibilidad y disponibilidad de capacidad productiva.

La fabricación en suelo estadounidense, además, tiene lectura política. Para administraciones con agendas de reindustrialización, disponer de un actor capaz de ofrecer nodos avanzados de proceso y empaquetado de alto nivel dentro de las fronteras es una baza estratégica de primer orden.

EMIB y EMIB-T frente a CoWoS: costes, tiempos y flexibilidad

Comparar EMIB-T con CoWoS no es trivial, porque ambos apuntan a objetivos similares con filosofías distintas. CoWoS se basa en un interposer de silicio de gran tamaño sobre el que se montan las matrices de cómputo y la memoria HBM. Esta solución ofrece un ancho de banda brutal y una densidad de interconexión altísima, pero también implica costos muy elevados, complejidad de fabricación y límites físicos en el tamaño del propio interposer.

EMIB y EMIB-T, en cambio, apuestan por puentes embebidos localizados, repartidos por el sustrato solo allí donde se necesitan. Esto simplifica parte del proceso y reduce la necesidad de manejar trozos de silicio tan grandes, con el consiguiente ahorro potencial en coste y mayor margen de maniobra para el diseño. A cambio, el ancho de banda máximo alcanzable puede ser, en ciertos casos, inferior al de un gigantesco interposer dedicado, aunque suficiente para muchísimas aplicaciones de IA y HPC.

En un momento en el que la demanda de CoWoS supera claramente la oferta, algunos clientes valoran más poder tener un proveedor alternativo con capacidad libre que exprimir el último gigabyte por segundo posible. Desde este prisma, EMIB se presenta como un compromiso muy práctico: ancho de banda elevado, latencias bajas, buena eficiencia térmica y, sobre todo, disponibilidad industrial inmediata sin colas interminables.

Para Intel, la jugada es doble. Por un lado, atrae proyectos de empaquetado avanzado con márgenes altos. Por otro, utiliza EMIB y EMIB-T como “puerta de entrada” para que esos mismos clientes, que hoy le encargan el backend, se animen a fabricar también sus obleas completas en sus futuros nodos avanzados como 18A o 14A. El empaquetado se convierte así en un gancho comercial clave para consolidar Intel Foundry Services.

En cualquier caso, lo que terminará decidiendo quién gana este pulso no será el marketing ni los renders espectaculares, sino la capacidad de repetir estos procesos de empaquetado avanzado a gran escala, con rendimientos aceptables y una cadena de suministro robusta. Si Intel demuestra que puede hacerlo de forma sostenida, EMIB-T tiene muchas papeletas para convertirse en una alternativa sólida frente a las soluciones consolidadas de TSMC.

Visto todo lo anterior, EMIB y especialmente EMIB-T representan para Intel mucho más que una tecnología de nicho: son el eje de una estrategia para recuperar relevancia en el negocio mundial de semiconductores en plena era de la inteligencia artificial. Entre la necesidad de superar la limitación de la retícula, el auge de arquitecturas chiplet, la saturación de CoWoS y las tensiones geopolíticas, los puentes de silicio embebidos de Intel se sitúan como una de las piezas que pueden inclinar la balanza del futuro del empaquetado avanzado, siempre que la compañía logre materializar en contratos firmes y producción masiva los rumores que hoy la rodean.