- Diseño de un sumador binario de 8 bits sin signo con bit de acarreo, base de muchas prácticas en FPGA.

- Implementaciones equivalentes en VHDL, Verilog y Chisel usando operadores aritméticos y tipos adecuados.

- Integración del sumador en tarjetas FPGA de entrenamiento con interruptores, LEDs y displays de 7 segmentos.

- Uso del sumador de 8 bits como bloque didáctico para aprender síntesis digital, asignación de pines y representación numérica.

En diseño digital, un sumador binario de 8 bits es uno de esos bloques básicos que te vas a encontrar en prácticamente cualquier sistema con FPGA o ASIC: desde proyectos académicos sencillos hasta procesadores más serios. Dominarlo en distintos lenguajes de descripción de hardware (HDL) como VHDL, Verilog y Chisel es clave para desenvolverte con soltura cuando pases del papel a la implementación real.

Los documentos que suelen circular por la red sobre “sumador de 8 bits en VHDL” se centran casi siempre en el mismo caso: un sumador binario sin signo, implementado en una tarjeta de entrenamiento FPGA (muy típico ver placas tipo DE2-115 o similares), con los operandos introducidos mediante switches y el resultado mostrado en displays de 7 segmentos o en LEDs. A partir de esa idea base, aquí vamos a explicarlo con más calma, en castellano de andar por casa, y completándolo con ejemplos claros en VHDL, Verilog y Chisel.

Conceptos básicos del sumador binario de 8 bits

Un sumador binario de 8 bits toma dos operandos A y B de 8 bits cada uno (normalmente sin signo) y genera una salida de 8 bits (la suma) más un bit de acarreo de salida (carry out). Es decir, si A y B van de 0 a 255, la suma puede ir de 0 a 510, así que el resultado ocupa potencialmente 9 bits.

En los proyectos didácticos típicos, el sumador se implementa como un bloque combinacional puro: la salida depende únicamente de las entradas, sin registros internos ni reloj. A nivel lógico, se utiliza la operación de suma definida en los paquetes estándar de tipos aritméticos del lenguaje (por ejemplo, numeric_std en VHDL) o bien se compone el sumador a partir de sumadores completos de un bit en cadena.

Cuando este diseño se lleva a una tarjeta FPGA de laboratorio, lo habitual es asignar cada bit de los operandos a un interruptor de la placa, y mostrar el valor resultante en LEDs o displays de 7 segmentos. Los documentos que mencionas describen justo este entorno: una tarjeta FPGA tipo D2-115 (o similar), con un archivo de asignación de pines que mapea entradas y salidas del HDL hacia los conectores físicos.

En algunos casos se aprovecha el ejercicio para repasar también la conversión de binario a BCD (decimal codificado en binario) y su posterior visualización, ya que los displays de 7 segmentos muestran cifras decimales y no directamente números binarios de 8 bits.

Arquitectura del sumador: desde el bit hasta los 8 bits

Antes de entrar en código, conviene entender cómo se construye un sumador completo de 1 bit y cómo se encadenan varios para obtener un sumador de 8 bits. Este enfoque es el que suelen seguir los diagramas de bloques de las tarjetas de entrenamiento FPGA.

Un sumador completo de 1 bit recibe tres entradas: A, B y el acarreo de entrada Cin. Devuelve dos salidas: la suma de ese bit (S) y el acarreo de salida (Cout). Las ecuaciones lógicas típicas son:

S = A XOR B XOR Cin

Cout = (A AND B) OR (Cin AND (A XOR B))

Si encadenas ocho de estos sumadores completos, pasas el acarreo de salida de cada uno como acarreo de entrada al siguiente. El primer sumador (bit 0) suele tener el acarreo de entrada a 0, salvo que quieras sumar también un posible bit de acarreo previo.

Desde el punto de vista de síntesis en una FPGA moderna, muchas veces no hace falta describir la estructura de sumadores completos explícitamente: basta con usar el operador + sobre tipos adecuados (por ejemplo, unsigned en VHDL), y será el propio sintetizador el que genere la lógica del sumador, optimizada para los recursos internos de la FPGA (LUTs, carry chains, etc.).

En las prácticas que mencionan las fuentes, es normal ver el sumador integrado en un diagrama de bloques dentro de la herramienta de la FPGA (Quartus, Vivado, etc.), o bien como una entidad/ módulo reutilizable que se conecta a otros módulos encargados de la visualización en displays de 7 segmentos.

Ejemplo de sumador binario de 8 bits en VHDL

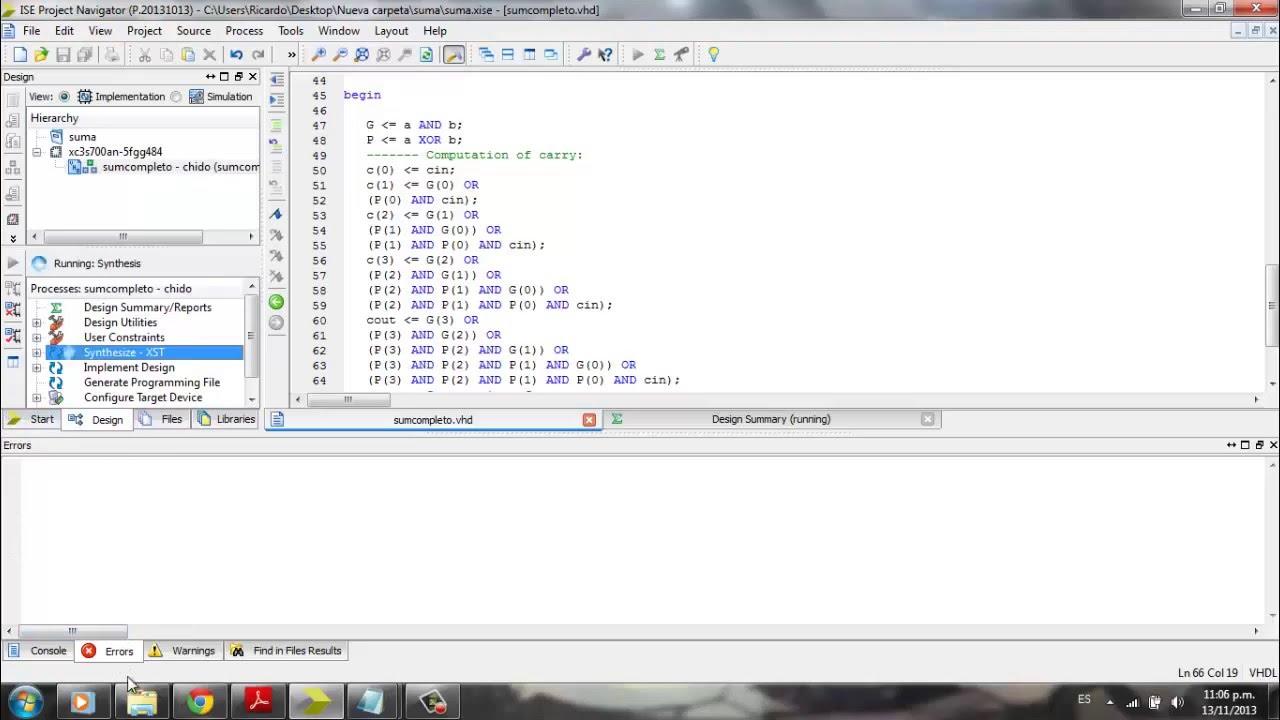

Los documentos originales giran sobre todo alrededor de un sumador de 8 bits en VHDL, implementado en una placa de entrenamiento FPGA, normalmente con operandos sin signo. Aunque cada autor cambia nombres y detalles, la estructura básica suele ser muy parecida a esta.

Primero, se declaran las librerías y el uso de paquetes aritméticos apropiados, como ieee.std_logic_1164 y ieee.numeric_std, que permiten trabajar cómodamente con vectores de bits y operaciones de suma:

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity sumador8_vhdl is

port(

A : in std_logic_vector(7 downto 0);

B : in std_logic_vector(7 downto 0);

SUM : out std_logic_vector(7 downto 0);

COUT : out std_logic

);

end entity sumador8_vhdl;

En el cuerpo de la arquitectura se suele hacer la suma con tipos unsigned, que representan enteros sin signo. De ese modo, la suma es directa y el sintetizador infiere la lógica del sumador:

architecture rtl of sumador8_vhdl is

signal a_u, b_u : unsigned(7 downto 0);

signal result_u : unsigned(8 downto 0);

begin

a_u <= unsigned(A);

b_u <= unsigned(B);

result_u <= ('0' & a_u) + ('0' & b_u);

SUM <= std_logic_vector(result_u(7 downto 0));

COUT <= result_u(8);

end architecture rtl;

En el tipo de prácticas documentadas en las fuentes, las señales A y B suelen conectarse a bancos de interruptores físicos de la FPGA (por ejemplo, SW[7..0] y SW[15..8]), mientras que la salida SUM se asocia a LEDs o a la entrada de un módulo de conversión a BCD para mostrar el resultado en los displays de 7 segmentos.

Algunas guías también explican cómo mapear la suma a BCD para poder mostrar los valores decimales. Este paso suele hacerse con algoritmos tipo “double dabble” o módulos ya preparados que convierten de binario a BCD, y se dejan como bloques separados para no mezclar la lógica del sumador con la del display.

En la implementación práctica en FPGA, además del código VHDL del sumador, tendrás un archivo de asignación de pines donde se definen qué bits de std_logic_vector van conectados a qué pin físico de la FPGA (por ejemplo, al conector de un display o a un LED).

Sumador de 8 bits en Verilog: ejemplo equivalente

Pasar de VHDL a Verilog para este tipo de sumadores es bastante directo. En lugar de trabajar con tipos aritméticos como unsigned, normalmente utilizas directamente vectores de bits y dejas que el compilador interprete el operador + como suma sin signo, salvo que especifiques otra cosa.

Un módulo Verilog típico para un sumador binario de 8 bits sin signo podría verse así:

module sumador8_verilog (

input [7:0] A,

input [7:0] B,

output [7:0] SUM,

output COUT

);

wire [8:0] result;

assign result = {1'b0, A} + {1'b0, B};

assign SUM = result[7:0];

assign COUT = result[8];

endmodule

Aquí se hace algo análogo a lo que se veía en VHDL: se amplían los operandos A y B con un bit adicional a 0 por la parte más significativa, se realiza la suma y se obtiene un resultado de 9 bits, donde result[7:0] es la suma y result[8] es el bit de acarreo de salida.

En muchas tarjetas de entrenamiento FPGA se trabaja con diagramas de bloques donde se instancian módulos Verilog como si fuesen bloques lógicos conectados entre sí. El sumador de 8 bits se integra como un bloque más, junto con módulos de control, contadores, convertidores de binario a BCD, controladores de display, etc.

Desde el punto de vista de síntesis, la herramienta (Quartus, Vivado, etc.) reconocerá el patrón de suma y utilizará las cadenas de acarreo internas de la FPGA, creando un sumador rápido y eficiente en recursos, equivalente al que se obtendría en VHDL.

Si quisieras trabajar con números con signo, tendrías que declarar los buses como signed (en SystemVerilog, por ejemplo) o dejar claro en la documentación que, aunque el tipo sea sin signo, estás interpretando los bits en complemento a dos. Sin embargo, en la mayoría de prácticas inspiradas en las fuentes, se maneja el caso sin signo puro para simplificar.

Sumador binario de 8 bits en Chisel

Chisel es un lenguaje de descripción de hardware de más alto nivel, basado en Scala, que permite describir circuitos de forma más estructurada y reutilizable. Aunque las fuentes originales que comentas se centran en VHDL y en la implementación en FPGA mediante diagramas de bloques, es perfectamente razonable considerar también un ejemplo equivalente en Chisel para el mismo sumador de 8 bits.

El enfoque típico en Chisel es declarar un módulo con entradas y salidas tipadas, y usar los operadores aritméticos directamente sobre esos tipos. Un ejemplo sencillo de sumador de 8 bits sin signo sería el siguiente:

import chisel3._

class Sumador8Chisel extends Module {

val io = IO(new Bundle {

val A = Input(UInt(8.W))

val B = Input(UInt(8.W))

val SUM = Output(UInt(8.W))

val COUT = Output(Bool())

})

val result = Wire(UInt(9.W))

result := io.A.zext() +& io.B.zext()

io.SUM := result(7, 0)

io.COUT := result(8)

}

En este código, se utiliza UInt(8.W) para representar enteros sin signo de 8 bits. La operación +& en Chisel genera una suma con bit de acarreo, produciendo un resultado de 9 bits si los operandos son de 8. Después se separa la parte baja (8 bits de suma) y el bit más significativo como acarreo.

En un flujo de trabajo típico con Chisel, este módulo se genera a Verilog, y luego se usa esa salida Verilog como parte del diseño que será sintetizado en la FPGA. Desde la perspectiva de la FPGA, da igual que el punto de partida fuese VHDL, Verilog directamente o Chisel: al final, la lógica sintetizada será un sumador binario de 8 bits con su correspondiente acarreo de salida.

Si quisieras reproducir el entorno de laboratorio de las fuentes (interruptores, LEDs, displays de 7 segmentos, etc.), en Chisel describirías módulos adicionales que conectasen la lógica del sumador con los pines de entrada/salida, pero conceptualmente el núcleo del sumador se mantiene igual de sencillo.

Integración en una tarjeta FPGA de entrenamiento

La configuración típica incluye:

- Entradas A y B: conectadas a dos grupos de interruptores (SW) de 8 bits cada uno.

- Resultado binario: bien en un conjunto de LEDs (8 bits) o como entrada a un conversor binario-BCD.

- Acarreo de salida (COUT): mapeado a un LED independiente para indicar desbordamiento.

- Displays de 7 segmentos: para mostrar A, B y/o la suma en formato decimal, utilizando módulos de conversión de binario a BCD y de BCD a segmentos.

El proyecto completo en la herramienta de la FPGA (por ejemplo, Quartus) suele organizarse en varios niveles: en el nivel más bajo está el sumador de 8 bits, y por encima se añaden los módulos de interfaz usuario-hardware, que se ocupan de la visualización y la lectura de las entradas.

En muchos casos, estos diseños se representan también como diagramas de bloques, donde el sumador es un bloque rectangular con sus puertos A, B, SUM y COUT, y se conecta mediante cables a bloques de decodificación para los displays de 7 segmentos y otros componentes.

Los PDFs que circulan sobre el tema suelen incluir además esquemas de la asignación de pines, mostrando qué nombre HDL (por ejemplo A(0), SUM(7), COUT) se corresponde con qué pin físico de la FPGA y con qué elemento de la placa (interruptor, LED, segmento de display…).

Cuando se quiere ir un poco más allá, se introduce la representación en BCD (decimal codificado en binario) para mostrar la suma en decimal. En este caso, el resultado de 8 bits del sumador se pasa a un módulo conversor binario-BCD, que genera dígitos decimales que luego son dirigidos a cada display de 7 segmentos.

Todo este circuito, aunque pueda parecer algo complejo a primera vista, descansa en un núcleo muy sencillo: la lógica del sumador de 8 bits, que es justo lo que hemos descrito en VHDL, Verilog y Chisel.

Visto en conjunto, el sumador binario de 8 bits funciona como una especie de “laboratorio reducido” para practicar con entrada/salida digital, representación numérica y manejo de herramientas de síntesis y asignación de pines, aprovechando un ejemplo fácil de entender pero suficientemente completo para cubrir muchos conceptos de diseño digital.

Con estos bloques básicos claros (sumador, acarreo, tipos sin signo, integración en FPGA y visualización en binario y BCD), resulta mucho más sencillo dar el salto a diseños más grandes como ALUs completas, procesadores simples o módulos de cálculo más complejos que reutilizan la misma lógica fundamental vista aquí.