- El TDDB describe la ruptura progresiva del dieléctrico de puerta por generación estocástica de defectos bajo estrés eléctrico y térmico.

- El grosor y el material del óxido, junto con los modelos E, 1/E y de ley de potencia, determinan la predicción del tiempo hasta el fallo.

- El TDDB es un mecanismo clave de desgaste en la curva de bañera y está estrechamente ligado al envejecimiento global de los transistores.

- Ensayos de estrés constante, control de proceso y estrategias de diseño permiten mitigar el TDDB y mejorar la fiabilidad de los circuitos integrados.

En el diseño de circuitos integrados modernos, la fiabilidad de los materiales aislantes y el envejecimiento de los transistores se han convertido en un auténtico quebradero de cabeza. A medida que las tecnologías se vuelven más pequeñas y complejas, los campos eléctricos aumentan, las capas dieléctricas se afinan al límite y cualquier pequeño defecto puede acortar de forma dramática la vida útil de un chip.

Dentro de todos los mecanismos de degradación, uno sobresale por su impacto directo en la vida útil de los dispositivos: el Time-Dependent Dielectric Breakdown (TDDB) o ruptura dieléctrica dependiente del tiempo. Entender cómo se generan los defectos en el óxido de puerta, cómo conduce eso a una ruptura y cómo se relaciona con el envejecimiento general de los transistores es fundamental para cualquiera que diseñe, fabrique o integre sistemas electrónicos de alta fiabilidad.

Qué es el Time-Dependent Dielectric Breakdown (TDDB)

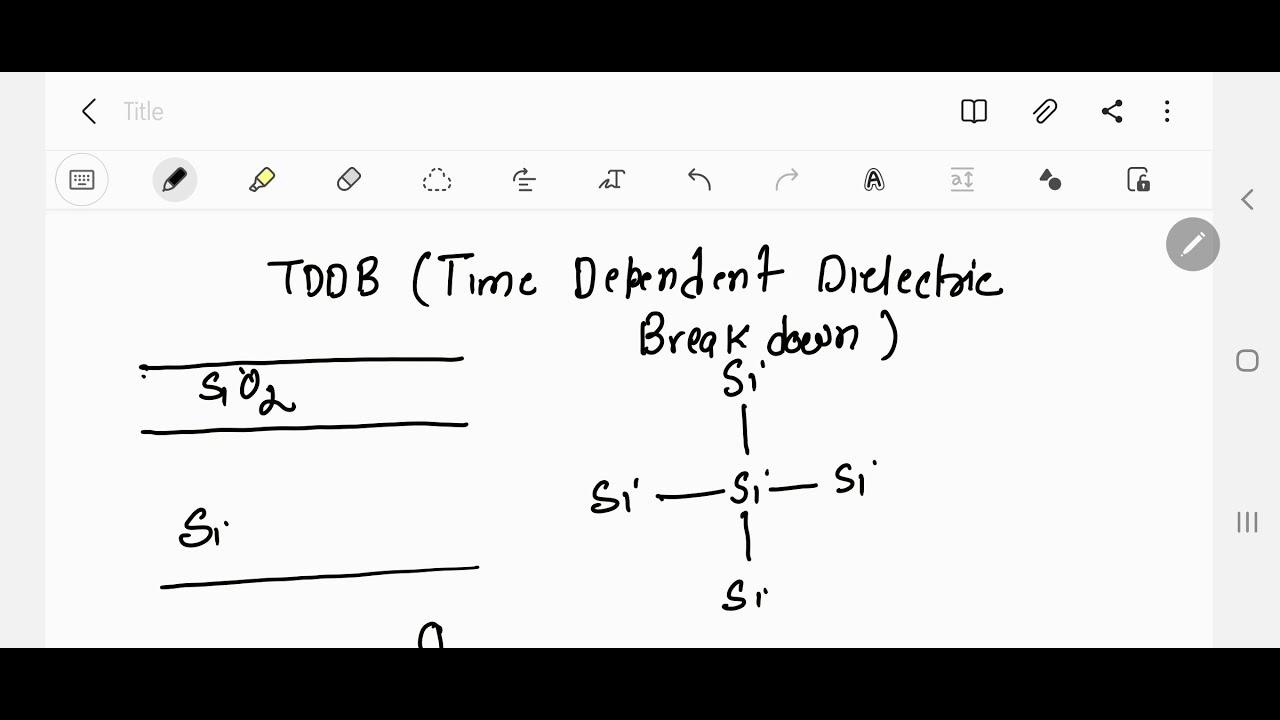

El TDDB es un fenómeno por el cual un material dieléctrico sometido a un campo eléctrico constante se va degradando de forma progresiva hasta perder su capacidad aislante. En los transistores MOSFET de los circuitos integrados, ese dieléctrico suele ser el óxido de puerta que separa el canal del electrodo de puerta. Durante la vida operativa del dispositivo, el campo eléctrico y la temperatura favorecen la generación de defectos en el óxido, y tras un cierto tiempo aparece un camino conductivo que provoca la ruptura.

En lugar de producirse de golpe al superar un voltaje crítico, la ruptura asociada al TDDB es un proceso estocástico o aleatorio de generación de defectos. Cada dispositivo experimenta una evolución distinta, de manera que los tiempos de fallo no son todos iguales: se distribuyen estadísticamente. Esto hace que el TDDB se estudie desde la óptica de la fiabilidad y la estadística, utilizando distribuciones de tiempo hasta el fallo, extrapolaciones y modelos físicos que relacionan campo eléctrico, grosor del óxido, temperatura y material.

Conviene diferenciar el TDDB de una ruptura inmediata por sobrepasar el voltaje máximo del dieléctrico. En TDDB el óxido puede operar inicialmente dentro de sus límites nominales, pero la exposición prolongada a ese estrés termina creando suficientes defectos como para que la corriente de fuga se dispare y el aislamiento se pierda de forma irreversible.

En la práctica, cuando se habla de TDDB se está describiendo uno de los mecanismos de desgaste intrínsecos más importantes en semiconductores, estrechamente vinculado con el aging o envejecimiento de los transistores. Este fenómeno se vuelve especialmente crítico en nodos avanzados, donde las capas de óxido son extremadamente delgadas y el margen de seguridad es muy reducido.

Modos de ruptura: intrínseca y extrínseca

El proceso de generación de defectos en un dieléctrico es inherentemente aleatorio, pero no todas las rupturas del óxido tienen el mismo origen físico. Tradicionalmente se distinguen dos modos de ruptura: la intrínseca y la extrínseca, cada una con sus causas dominantes y sus implicaciones para el diseño y el proceso de fabricación.

La ruptura intrínseca está asociada al propio estrés eléctrico aplicado durante la operación del dispositivo. A medida que se mantiene un campo eléctrico elevado a través del óxido, se generan defectos en la red cristalina o en las interfaces. Estos defectos actúan como trampas de carga y puntos débiles que, con el tiempo, se conectan formando un camino de conducción a través del dieléctrico. Es un mecanismo de desgaste natural: aunque el proceso de fabricación fuera perfecto, bajo condiciones de uso suficientemente exigentes aparecería este tipo de fallo.

La ruptura extrínseca, en cambio, tiene su origen en defectos derivados del proceso de fabricación: partículas, impurezas, no uniformidades en el grosor del óxido o daños locales generados durante etapas de litografía, grabado o deposición. Estos defectos preexistentes reducen drásticamente el tiempo hasta la ruptura, ya que el óxido no parte de un estado ideal. A menudo están relacionados con la fase de «mortalidad infantil» de los productos, donde fallan prematuramente dispositivos con defectos de fabricación.

En el contexto de los circuitos integrados, ambos modos coexisten. Los fallos extrínsecos se intenta minimizar mediante una mejora continua del proceso, controles estrictos de partículas y medidas de calidad. Una vez reducido ese componente, el TDDB intrínseco pasa a dominar el final de vida útil de la población de dispositivos, siendo entonces el factor clave para estimar cuánto tiempo puede funcionar un chip bajo determinadas condiciones de tensión y temperatura.

La separación entre ruptura intrínseca y extrínseca también tiene impacto en el modelado. Mientras la parte extrínseca se asocia a la «cola temprana» de la distribución de fallos, la intrínseca marca la región de desgaste progresivo. Para que un diseño sea competitivo, los ingenieros buscan desplazar ambas regiones muy por encima del tiempo de vida requerido por la aplicación, ya sea electrónica de consumo, automoción o aplicaciones médicas.

Influencia del grosor y del material del óxido de puerta

Uno de los parámetros clave que determina la fiabilidad frente a TDDB es el grosor de la capa dieléctrica y el tipo de material empleado. En tecnologías CMOS antiguas, con grosores de óxido de puerta superiores a unos 4 nm, el material base era prácticamente siempre dióxido de silicio (SiO2). Este óxido térmico presenta unas propiedades muy estudiadas y relativamente robustas frente a la ruptura.

A medida que los nodos tecnológicos han ido escalando, reducir el grosor del óxido de puerta por debajo de aproximadamente 4 nm usando SiO2 puro se vuelve inviable, porque la corriente de túnel y las fugas se disparan. Para mantener la capacitancia de puerta necesaria sin seguir adelgazando físicamente el dieléctrico, la industria adoptó materiales de alta constante dieléctrica, conocidos como high-k. Estos materiales permiten una capacitancia equivalente a un óxido de SiO2 muy fino, pero con un grosor físico mayor, reduciendo así la fuga estática.

El cambio de SiO2 a materiales high-k, sin embargo, introduce nuevos retos en términos de TDDB. Las propiedades de generación de defectos, la movilidad de vacantes de oxígeno, las interfaces con el silicio y los electrodos metálicos hacen que los modelos clásicos deban ajustarse o replantearse. Además, la variabilidad de proceso y la calidad de las interfaces juegan un papel incluso más crítico que en las generaciones anteriores de óxido puro.

El grosor del óxido condiciona también qué modelos de TDDB resultan aplicables. En óxidos más gruesos y con campos moderados, ciertos modelos se ajustan mejor a los datos experimentales; en capas ultra delgadas, el transporte por túnel, la percolación de defectos y otros efectos dominan. Por eso, en cada nodo tecnológico se reevalúan los parámetros de los modelos y la estrategia de test de fiabilidad para garantizar que las extrapolaciones a condiciones de uso reales sean fiables.

En la investigación actual sobre nuevos materiales (por ejemplo, óxidos ferroelectricos como HfZrO o HZO), el TDDB es un aspecto central. La presencia de vacantes de oxígeno, los estados ferroelectricos y el grosor de la película influyen de manera compleja en el tiempo hasta la ruptura, por lo que se requieren estudios específicos de fiabilidad y modelos adaptados a estos nuevos dieléctricos.

Modelos de ruptura y comportamiento frente al campo eléctrico

Para poder predecir el tiempo hasta el fallo y diseñar especificaciones de tensión y temperatura, se recurre a modelos matemáticos que relacionan el estrés eléctrico con la vida útil del óxido. Entre los más utilizados se encuentran el modelo E, el modelo 1/E y las formulaciones de ley potencial de tipo exponencial. Cada uno intenta capturar la dependencia del tiempo hasta la ruptura con el campo eléctrico aplicado.

El denominado modelo E asume una dependencia exponencial del tiempo de vida con el campo eléctrico. Según este enfoque, pequeñas variaciones en el campo pueden tener un impacto enorme en el tiempo hasta la ruptura, lo que obliga a definir márgenes de diseño bastante conservadores. Este modelo suele ajustar bien datos de determinados rangos de grosor y campos.

El modelo 1/E, por su parte, plantea que la tasa de generación de defectos está inversamente relacionada con el campo. La dependencia del tiempo de fallo con 1/E aparece en muchas bases de datos experimentales, sobre todo en ciertos grosores de óxido y configuraciones de prueba específicas. En la práctica, ambos modelos se comparan frente a los datos de test para seleccionar el que mejor representa la realidad de una tecnología concreta.

Además, existen modelos de ley de potencia y formulaciones exponenciales más complejas que tienen en cuenta no solo el campo, sino también la temperatura, la distribución de defectos y hasta la física de percolación. Estos modelos se utilizan para extrapolar resultados de pruebas aceleradas (con campos y temperaturas muy por encima de los de uso real) hacia las condiciones normales de operación, donde se esperan tiempos de vida de años o incluso décadas.

La elección del modelo no es un detalle menor: de ella dependen los márgenes de diseño, las garantías de fiabilidad y las especificaciones de producto. Si el modelo escogido subestima la sensibilidad al campo o a la temperatura, el producto podría fallar antes de lo previsto en aplicaciones críticas. Por eso, los fabricantes realizan extensas campañas de caracterización y comparan distintos enfoques hasta encontrar el que mejor reproduzca la realidad estadística de sus óxidos.

Curva de bañera y papel del TDDB en la fiabilidad de los IC

La fiabilidad de los componentes de un circuito integrado suele representarse con la clásica curva de bañera (bathtub curve), que describe la tasa de fallos a lo largo del tiempo. Esta curva combina tres regiones bien diferenciadas: mortalidad infantil, periodo de fallos aleatorios y fase de desgaste o envejecimiento.

En la primera etapa, denominada mortalidad infantil, la tasa de fallos desciende con el tiempo. Aquí dominan los defectos de fabricación o de ensamblado: partículas, uniones defectuosas, óxidos con inclusiones extrínsecas, etc. Mediante cribados de producción y tests de burn-in se intenta que estos dispositivos defectuosos fallen antes de llegar al cliente.

En el tramo central de la curva se observa una tasa de fallos aproximadamente constante. Son fallos aleatorios, muchas veces debidos a eventos externos (como radiación ionizante) o defectos latentes que se manifiestan de manera aislada. Desde el punto de vista de diseño de fiabilidad, esta región se considera «estable» y se suele dimensionar para que la tasa de fallos cumpla con las especificaciones del mercado objetivo.

Finalmente llega la fase de wear-out o desgaste, en la que la tasa de fallos vuelve a incrementarse con el tiempo. Aquí entran en juego los mecanismos de envejecimiento intrínsecos del semiconductor: electromigración en metalizaciones, hot carrier injection, bias temperature instability (BTI) y, de forma destacada, el TDDB en las capas de óxido. Es en esta región donde el material empieza a acumular tantos defectos que la probabilidad de ruptura del óxido crece rápidamente.

El TDDB se considera, por tanto, uno de los mecanismos de desgaste intrínsecos más relevantes en la etapa final de vida de los IC. La capacidad de predecir el tiempo hasta el fallo asociado al TDDB para unas condiciones de uso concretas permite a los ingenieros fijar la vida útil garantizada del producto, definir temperaturas máximas de trabajo y márgenes de tensión aceptables, especialmente en aplicaciones de alta fiabilidad como automoción o aeroespacial.

Relación entre TDDB y envejecimiento de transistores

Cuando se habla de «transistor aging», normalmente se hace referencia al conjunto de mecanismos que degradan poco a poco las características eléctricas de los dispositivos. Algunos de estos mecanismos modifican parámetros como la tensión umbral, la movilidad o la transconductancia mucho antes de que se produzca un fallo catastrófico, mientras que otros están ligados a fallos abruptos, como la ruptura del óxido.

El TDDB forma parte de este abanico de fenómenos de envejecimiento. En transistores MOS, a medida que el óxido de puerta acumula defectos, puede aumentar la corriente de fuga y degradarse la integridad del aislamiento. Aunque en muchas aplicaciones se considera «fallo» el momento de ruptura completa del dieléctrico, en otras basta una cierta degradación para provocar un comportamiento fuera de especificación, sobre todo en circuitos analógicos o RF muy sensibles.

Junto al TDDB, otros mecanismos como el BTI (Bias Temperature Instability), la inyección de portadores calientes (Hot Carrier Injection) o la electromigración en interconexiones metálicas contribuyen al envejecimiento global del chip. En conjunto, definen la ventana de tiempo durante la cual el dispositivo se mantiene dentro de los parámetros eléctricos previstos.

En nodos muy avanzados, donde las tensiones nominales apenas pueden reducirse más y los márgenes se estrechan, el impacto relativo del TDDB sobre la vida útil aumenta. Por ello, la simulación de envejecimiento de transistores incorpora modelos de TDDB y se utilizan herramientas de análisis de fiabilidad que permiten ver cómo evolucionarán los circuitos bajo distintos perfiles de carga, frecuencia y temperatura.

En el ámbito del diseño de sistemas completos, comprender esta relación entre TDDB y envejecimiento es clave para definir estrategias de sobredimensionamiento, redundancia o márgenes de seguridad. Al fin y al cabo, el objetivo es que el dispositivo siga cumpliendo su función durante toda la vida útil prevista, incluso teniendo en cuenta que sus transistores se irán degradando progresivamente.

Ensayos de TDDB: pruebas de esfuerzo constante

Para investigar el comportamiento del TDDB y obtener datos fiables para los modelos, se emplean ensayos acelerados de fiabilidad. El más común de ellos es el test de «constant stress» o estrés constante, que se puede implementar de diferentes maneras, siendo las más habituales el Constant Voltage Stress (CVS) y el Constant Current Stress.

En un ensayo de tensión constante (CVS), se aplica a la puerta del transistor (o a una estructura de test específica de óxido) una tensión fija, normalmente inferior a la tensión de ruptura instantánea, pero suficientemente alta como para acelerar la generación de defectos. Mientras se mantiene esta tensión, se monitoriza la corriente de fuga a través del óxido. Cuando se observa un incremento brusco de la corriente o un cambio de comportamiento que indica ruptura, se registra el tiempo hasta el fallo.

Este procedimiento se repite en un gran número de dispositivos idénticos para obtener una distribución estadística de tiempos de fallo. A partir de esta distribución se construyen gráficas de fiabilidad (por ejemplo, representaciones tipo Weibull) que permiten entender la dispersión de los tiempos de ruptura y separar, en la medida de lo posible, contribuciones intrínsecas y extrínsecas.

En el caso del estrés de corriente constante, se fija la corriente que atraviesa el dieléctrico y se observa la evolución del voltaje necesario para mantener ese nivel de corriente. La aparición de una discontinuidad o un salto característico indica la ruptura. Aunque en la industria se usa más habitualmente el CVS para TDDB, ambos enfoques proporcionan información complementaria sobre los mecanismos de fallo.

Con los datos de estos ensayos, se ajustan los modelos de campo (E, 1/E, leyes de potencia, etc.) y se extrapolan los tiempos de vida a condiciones de operación mucho más suaves, donde no es viable esperar físicamente a que el dispositivo falle. Así se pueden establecer especificaciones como tiempo medio hasta el fallo (MTTF), niveles de tensión máxima recomendados o limitaciones de temperatura para garantizar la fiabilidad requerida.

Estrategias de mitigación del TDDB en el diseño de IC

Conociendo el impacto del TDDB, la industria ha desarrollado diferentes estrategias para reducir el riesgo de ruptura del óxido y alargar la vida útil de los transistores. Estas medidas abarcan desde la elección de materiales hasta el diseño de circuitos y el control del proceso de fabricación.

En primer lugar, la innovación en materiales juega un papel esencial. El uso de dieléctricos high-k bien optimizados, óxidos ferroelectricos para memorias no volátiles o estructuras multicapa con barreras de difusión busca mejorar tanto el rendimiento eléctrico como la robustez frente a la generación de defectos. El control de la concentración de vacantes de oxígeno y de las interfaces metal/dieléctrico es especialmente importante para limitar la formación de rutas conductivas.

Desde el punto de vista del diseño de circuitos, se persigue minimizar el estrés sobre los dieléctricos. Esto incluye elegir niveles de tensión de alimentación adecuados, repartir las caídas de tensión para evitar que un único dispositivo soporte el máximo estrés, y diseñar arquitecturas que limiten los picos de tensión transitorios. En aplicaciones donde se prevean voltajes altos o condiciones extremas, se puede recurrir a sobredimensionar ciertas zonas o usar transistores específicos más robustos.

En el ámbito del proceso de fabricación, mantener una gran uniformidad del grosor del óxido, reducir al mínimo las partículas y controlar con precisión las etapas de deposición y tratamiento térmico son aspectos críticos. Un proceso bien afinado disminuye la probabilidad de defectos extrínsecos que puedan provocar rupturas tempranas y mejora la repetibilidad de los tiempos de fallo intrínsecos, facilitando el diseño de márgenes fiables.

Finalmente, las pruebas de fiabilidad y la monitorización continua se han convertido en herramientas estratégicas. Ensayos como el TDDB, QBD (carga hasta la ruptura) o HTOL (High-Temperature Operating Life) permiten validar que los objetivos de fiabilidad se cumplen antes del lanzamiento del producto. Además, en algunos casos se emplean sensores integrados y técnicas de supervisión en tiempo real para detectar degradación temprana y anticipar fallos en sistemas críticos.

Todo este conjunto de medidas se integra en lo que podría llamarse una «ingeniería de fiabilidad de óxido». El objetivo es encontrar el equilibrio óptimo entre rendimiento, consumo de potencia, área de silicio y vida útil garantizada, algo cada vez más delicado conforme los nodos tecnológicos se acercan a sus límites físicos.

El comportamiento frente al TDDB y su relación con el envejecimiento de los transistores condicionan de forma decisiva cómo se diseñan, fabrican y prueban los circuitos integrados actuales. Desde la elección del óxido de puerta y el modelo de ruptura, pasando por la forma de interpretar la curva de bañera, hasta la definición de ensayos de estrés y estrategias de mitigación, todo está orientado a conseguir que los chips soporten durante años el campo eléctrico y la temperatura de operación sin perder su integridad dielélectrica ni salirse de especificación. Entender a fondo este fenómeno permite no solo evitar fallos catastróficos, sino también optimizar el rendimiento y la competitividad de los productos en un sector donde cada nanómetro y cada voltio cuentan.