- UCIe estandariza la interconexión die a die para combinar chiplets de múltiples proveedores en un mismo paquete.

- Basado en PCIe y CXL, ofrece más de 1 TB/s y 0,25 pJ/bit, con soporte para empaquetado 2.5D y 3D.

- El consorcio incluye a AMD, ARM, Intel, Qualcomm, Samsung y TSMC, entre otros; NVIDIA no figura entre los fundadores.

- Permite diseños modulares, eficientes y escalables para CPUs, GPUs, APUs y SoCs en móvil, PC y centro de datos.

Si nunca has oído hablar de UCIe, no pasa nada: pronto será un término habitual cuando se hable de procesadores, APUs y SoCs, porque este estándar apunta a convertirse en el lenguaje común de los chips por piezas. Universal Chiplet Interconnect Express plantea una forma unificada de conectar chiplets dentro del mismo paquete, abriendo la puerta a colaboraciones entre fabricantes que hace poco parecían impensables.

Durante años hemos pasado de los diseños monolíticos —un único chip grande y complejo— a arquitecturas por módulos en las que varias matrices más pequeñas se reparten el trabajo. Ese enfoque por chiplets aumenta la modularidad y abarata costes, ya que gestionar defectos de fabricación es más sencillo cuando la lógica se divide en bloques más pequeños, y permite combinar funciones especializadas sin que todo dependa de un único troquel gigantesco.

Qué es UCIe y por qué importa

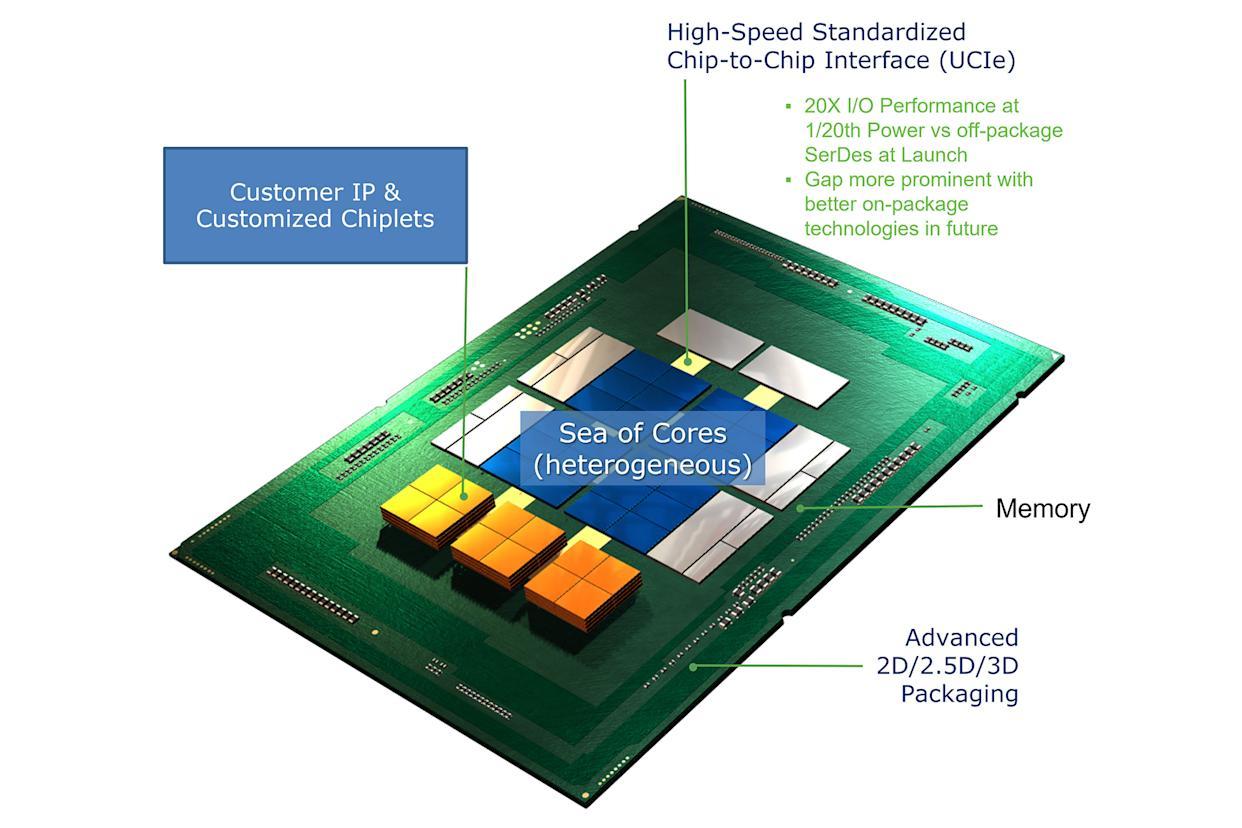

UCIe, siglas de Universal Chiplet Interconnect Express, es una especificación que define la interconexión die a die dentro de un mismo encapsulado. En la práctica, estandariza cómo se comunican y cooperan los chiplets, de modo que un diseñador de SoCs pueda integrar piezas de distintos orígenes sin reinventar la rueda para cada proyecto.

El valor de un estándar depende del respaldo de la industria, y aquí la lista impresiona: AMD, ARM, ASE (Advanced Semiconductor Engineering), Google Cloud, Intel, Meta, Microsoft, Qualcomm, Samsung y TSMC figuran entre los impulsores. Son los actores clave del diseño, el empaquetado y la fabricación de semiconductores, y su apoyo implica un empujón decisivo para la adopción. Curiosamente, NVIDIA no aparece entre los fundadores en este arranque.

La idea puede entenderse con una analogía del PC de toda la vida: conectas una gráfica, una tarjeta de sonido o una de red a la placa base y todo trabaja junto gracias a estándares comunes. Con UCIe se busca algo similar pero a escala de chip, permitiendo montar un SoC combinando chiplets especializados como si fuese un equipo a medida, pero dentro de un único paquete.

El enfoque chiplet no es nuevo. AMD lo popularizó en la gama Ryzen con diseños MCM (Multi-Chip Module), mientras que Intel lo aplica en su arquitectura gráfica Xe, entre otros proyectos. Esta tendencia responde a una lógica de divide y vencerás: funciones separadas, cada una en su chiplet, y comunicación interna de muy baja latencia y altísimo ancho de banda.

Además de la flexibilidad, hay ventajas en rendimiento, coste y escalabilidad. Los defectos de fabricación penalizan menos cuando el diseño se compone de varias matrices más pequeñas, y los fabricantes pueden actualizar bloques concretos sin rehacerlo todo. Y no es exclusivo del PC: los SoC de móviles y tablets llevan años aprovechando este paradigma modular.

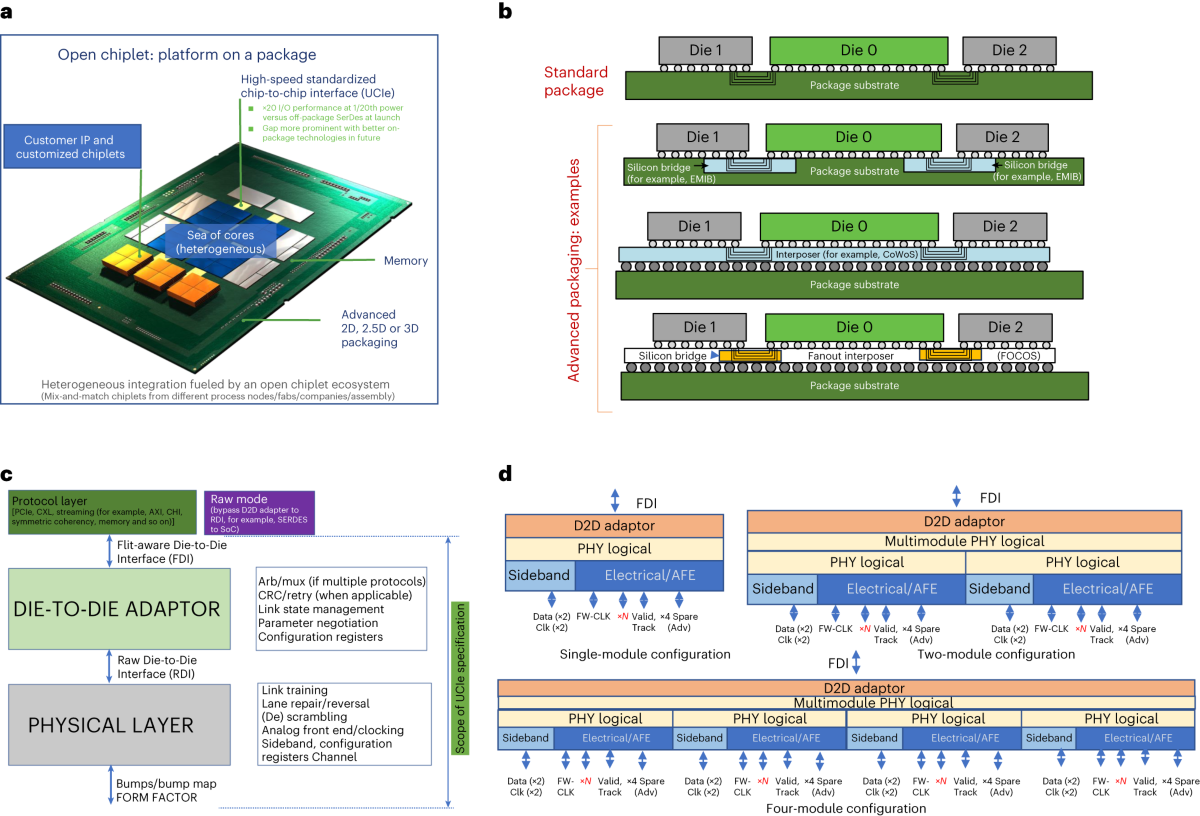

Especificación UCIe 1.0: fundamentos técnicos

Las empresas fundadoras han ratificado la versión inicial de la norma, UCIe 1.0. Esta especificación abierta abarca la capa física de I/O entre chips, los protocolos de comunicación y la pila de software, apoyándose en estándares consolidados como PCI Express (PCIe) y Compute Express Link (CXL). La documentación está disponible para los miembros del consorcio y es la base para un ecosistema interoperable.

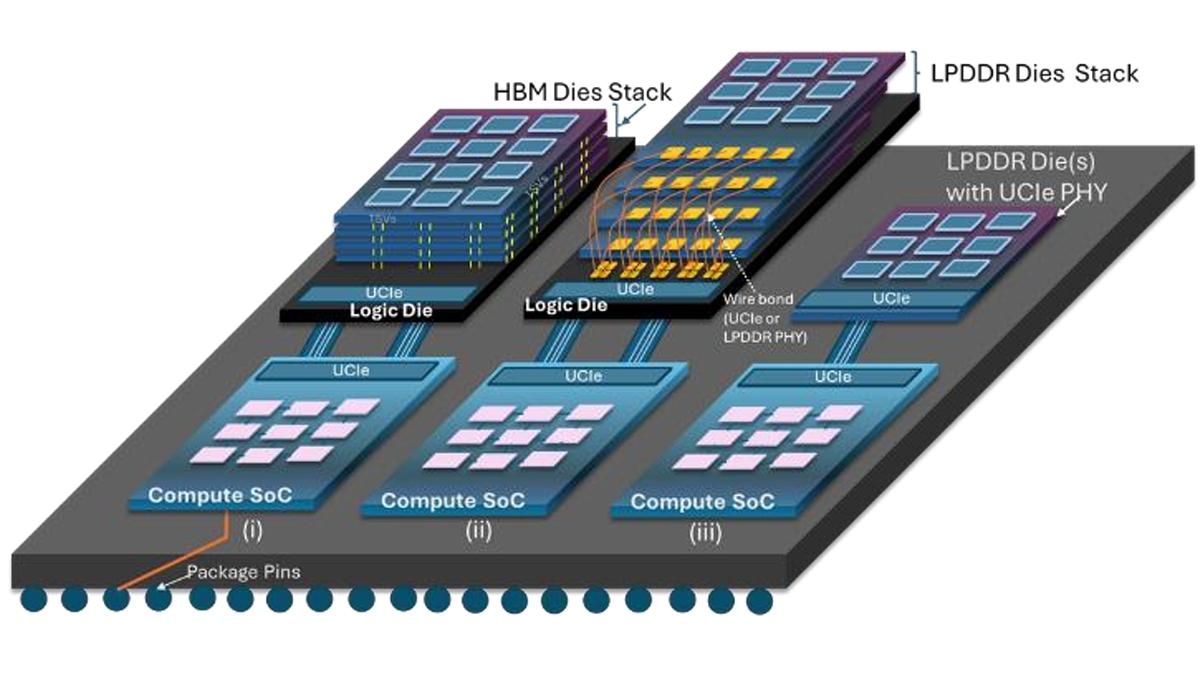

UCIe tiene en cuenta tanto arquitecturas 2.5D como 3D, lo que encaja con el auge del empaquetado avanzado que ya exploran varios fabricantes. La interconexión die a die puede implementarse con diferentes topologías sobre el interposer (el sustrato de comunicación sobre el que se montan los chiplets) e, incluso, mediante apilado vertical cuando el diseño lo exige.

En esta primera iteración el rendimiento no es un añadido menor: se plantean anchos de banda por encima del terabyte por segundo, una cifra que permite mover datos masivos entre bloques de cómputo y memoria dentro del encapsulado sin que la interconexión sea el cuello de botella.

La eficiencia energética de la interconexión es otro punto fuerte: en torno a 0,25 picojulios por bit transmitido (0,25 pJ/bit). Para ponerlo en contexto, la transferencia hacia RAM tradicional suele moverse, según el tipo de memoria, entre unos 6 y 8 pJ/bit de media. Esta diferencia es crítica en diseños con decenas de núcleos CPU en servidores, o en futuras GPU compuestas por varios chiplets.

La norma también perfila cómo encapsular protocolos de más alto nivel, de manera que la compatibilidad no dependa de soluciones ad hoc. Al apoyarse en PCIe y CXL, UCIe hereda una base probada para coherencia de memoria, latencias ajustadas y gestión de recursos compartidos entre elementos heterogéneos.

Los promotores señalan la existencia de dos modalidades de interconexión iniciales dentro del estándar, orientadas a cubrir escenarios habituales de montaje sobre interposer y opciones de apilado. No todos los proyectos necesitan la misma densidad o la misma distancia entre chiplets, así que la especificación habilita perfiles para casar rendimiento, consumo y coste del paquete.

Ecosistema y postura de las empresas

El consorcio que da forma a UCIe representa un abanico amplio de segmentos del mercado y responde a la demanda de integración personalizable a nivel de paquete. La ambición es conectar la mejor interconexión die a die con protocolos estándar y sentar las bases para un ecosistema realmente interoperable, con múltiples proveedores y sin ataduras propietarias innecesarias.

Desde AMD subrayan su trayectoria apoyando estándares abiertos y su liderazgo en tecnología de chiplets. Para la compañía, UCIe es clave para impulsar sistemas con motores de cómputo y aceleradores heterogéneos, optimizando el equilibrio entre rendimiento, coste y eficiencia energética en función de cada caso de uso.

ARM, por su parte, pone el foco en la interoperabilidad: reducir la fragmentación en el ecosistema es vital, y colaborar con otros líderes del sector en especificaciones como UCIe es una vía directa para habilitar los diseños de sistemas del futuro sin duplicar esfuerzos.

Intel enmarca esta transición en su estrategia IDM 2.0. Integrar múltiples matrices en un paquete para acelerar la innovación de producto es, en su visión, el futuro de la industria y un requisito para seguir cumpliendo la promesa de la Ley de Moore. Un ecosistema abierto de chiplets es imprescindible para ese avance.

Qualcomm destaca que la industria se una en torno a UCIe para hacer progresar la tecnología de chiplets. Es una pieza esencial para afrontar la complejidad creciente de los sistemas de semiconductores, donde cada bloque debe encajar con precisión en arquitecturas más ambiciosas.

Desde Samsung se anticipa que la tecnología de chiplets será necesaria para mejorar el rendimiento de los sistemas a medida que los nodos de proceso sigan escalando. Lo deseable es que las matrices acaben comunicándose con un lenguaje único. Además, como proveedor integral de memoria, lógica y fundición, la compañía aspira a contribuir activamente a perfeccionar la interfaz abierta en toda la industria.

TSMC incide en que el estándar ampliará el ecosistema para la integración a nivel de paquete. Su catálogo de tecnologías de silicio y de empaquetado ofrece múltiples rutas de implementación para dispositivos heterogéneos basados en UCIe, lo que facilitará que cada diseñador encuentre el encaje técnico y económico ideal.

No pasa desapercibido que NVIDIA, ausente entre los impulsores iniciales, no figura en el grupo fundador. Aunque eso no impide sumarse más adelante, su ausencia inicial es relevante en un panorama donde la aceleración gráfica y de IA es protagonista.

De los laboratorios al mercado: usos y escenarios

Con una especificación común, las posibilidades de diseño se multiplican. Imagina una APU en la que los núcleos de alto rendimiento sean de un proveedor, los de eficiencia de otro y la parte gráfica de un tercero, todo ello negociando latencia y ancho de banda con el mismo lenguaje dentro del paquete. Eso que hoy suena a ejercicio teórico puede acabar siendo un camino realista para personalizar SoCs.

Este enfoque no se limita al PC. Teléfonos, portátiles, centros de datos y vehículos conectados son candidatos a beneficiarse de arquitecturas más granulares, donde cada bloque evoluciona a su ritmo sin obligar a revalidar un troquel monolítico completo en cada salto de generación.

La modularidad también facilita combinar chiplets fabricados en distintos nodos de proceso. Se puede reservar el nodo más avanzado para la lógica crítica y dejar tareas auxiliares a procesos más maduros y económicos, con un impacto directo en coste y disponibilidad.

Además, UCIe favorece ecosistemas en los que varios proveedores puedan especializarse y competir en determinados tipos de chiplets (I/O, aceleración AI, cache dies, seguridad, etc.). La interoperabilidad eleva el listón y acelera la innovación porque obliga a los módulos a destacar por prestaciones reales, consumo y precio.

- Más rendimiento por vatio dentro del paquete, gracias a interconexiones de muy bajo consumo y alta densidad.

- Time-to-market más corto, al permitir reutilizar y combinar bloques probados en vez de diseñarlo todo desde cero.

- Resiliencia de la cadena de suministro, con alternativas multi-proveedor para funciones críticas.

Retos pendientes y próximos pasos

Pese al impulso, UCIe 1.0 es solo el punto de partida. La verdadera prueba será la interoperabilidad real: validaciones cruzadas, bancos de prueba y certificaciones que garanticen que los chiplets de A encajan con los de B sin sorpresas en latencia, señal o coherencia de memoria.

El empaquetado avanzado y la gestión térmica son variables de primera. Apilar o acercar matrices con densidades tan altas exige disciplina de diseño en potencia, disipación y fiabilidad a largo plazo. Aquí las tecnologías 2.5D y 3D, junto con interposers de última generación, jugarán un papel central.

También habrá que alinear licencias de IP, modelos de negocio y cadenas de suministro. Un ecosistema abierto de chiplets requiere reglas claras para proteger propiedad intelectual y garantizar suministro, además de acuerdos que faciliten integrar bloques de distintas casas con garantías comerciales.

En el frente del software, apoyarse en PCIe y CXL ayuda mucho, pero las pilas de gestión, drivers y herramientas de verificación deberán evolucionar para que los desarrolladores traten conjuntos heterogéneos de chiplets como un todo coherente, con una visión sólida de calidad de servicio y depuración.

La industria ya venía colaborando en piezas sueltas —ahí están las sinergias entre Intel y TSMC en algunos proyectos— y UCIe pone orden a esa colaboración elevándola a estándar. Si la adopción progresa, veremos catálogos de chiplets listos para integrar, perfiles de interconexión definidos y referencias de diseño que harán más predecible el rendimiento final de cada paquete.

El movimiento hacia chiplets es imparable por su lógica técnica y económica, y UCIe le aporta el pegamento que faltaba. Con anchos de banda superiores al terabyte por segundo y consumos por bit extremadamente bajos, este estándar tiene mimbres para convertirse en la base sobre la que se construyan CPUs, GPUs, APUs y SoCs de la próxima década, desde el móvil al supercomputador, con más opciones para fabricantes y más competencia para el usuario final.